Ethernet (ETH): media access control (MAC) with DMA controller RM0008

1009/1128 DocID13902 Rev 15

• TDES0: Transmit descriptor Word0

The application software has to program the control bits [30:26]+[23:20] plus the OWN

bit [31] during descriptor initialization. When the DMA updates the descriptor (or writes

it back), it resets all the control bits plus the OWN bit, and reports only the status bits.

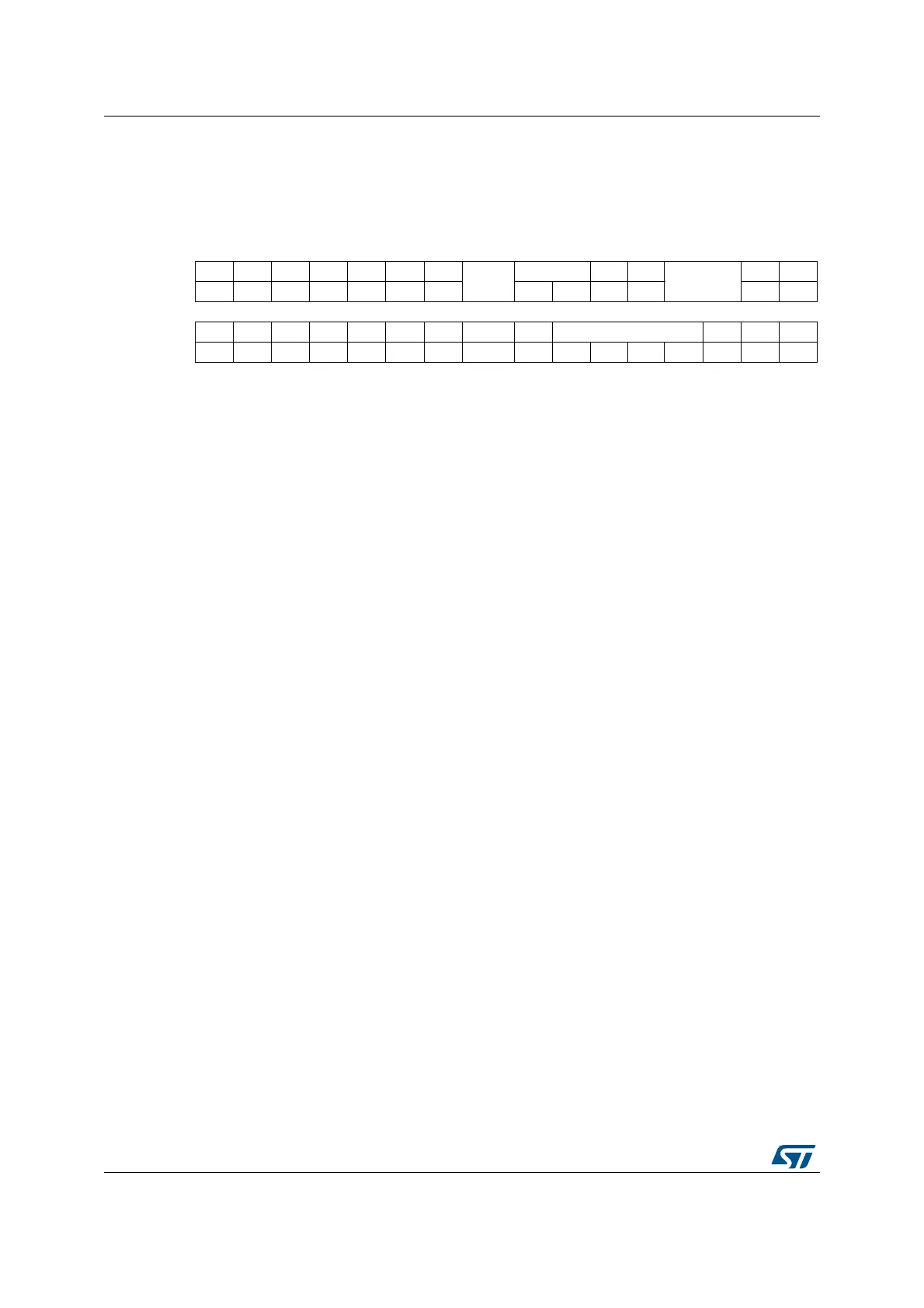

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

OWN IC LS FS DC DP TTSE

Res

CIC TER TCH

Res.

TTSS IHE

rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109 8 76543210

ES JT FF IPE LCA NC LCO EC VF CC ED UF DB

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 OWN: Own bit

When set, this bit indicates that the descriptor is owned by the DMA. When this bit is reset, it

indicates that the descriptor is owned by the CPU. The DMA clears this bit either when it

completes the frame transmission or when the buffers allocated in the descriptor are read

completely. The ownership bit of the frame’s first descriptor must be set after all subsequent

descriptors belonging to the same frame have been set.

Bit 30 IC: Interrupt on completion

When set, this bit sets the Transmit Interrupt (Register 5[0]) after the present frame has

been transmitted.

Bit 29 LS: Last segment

When set, this bit indicates that the buffer contains the last segment of the frame.

Bit 28 FS: First segment

When set, this bit indicates that the buffer contains the first segment of a frame.

Bit 27 DC: Disable CRC

When this bit is set, the MAC does not append a cyclic redundancy check (CRC) to the end

of the transmitted frame. This is valid only when the first segment (TDES0[28]) is set.

Bit 26 DP: Disable pad

When set, the MAC does not automatically add padding to a frame shorter than 64 bytes.

When this bit is reset, the DMA automatically adds padding and CRC to a frame shorter than

64 bytes, and the CRC field is added despite the state of the DC (TDES0[27]) bit. This is

valid only when the first segment (TDES0[28]) is set.

Bit 25 TTSE: Transmit time stamp enable

When TTSE is set and when TSE is set (ETH_PTPTSCR bit 0), IEEE1588 hardware time

stamping is activated for the transmit frame described by the descriptor. This field is only valid

when the First segment control bit (TDES0[28]) is set.

Bit 24 Reserved, must be kept at reset value.

Bits 23:22 CIC: Checksum insertion control

These bits control the checksum calculation and insertion. Bit encoding is as shown below:

00: Checksum Insertion disabled

01: Only IP header checksum calculation and insertion are enabled

10: IP header checksum and payload checksum calculation and insertion are enabled, but

pseudo-header checksum is not calculated in hardware

11: IP Header checksum and payload checksum calculation and insertion are enabled, and

pseudo-header checksum is calculated in hardware.

Loading...

Loading...