Universal synchronous asynchronous receiver transmitter (USART) RM0008

817/1128 DocID13902 Rev 15

Note: These 3 bits (CPOL, CPHA, LBCL) should not be written while the transmitter is enabled.

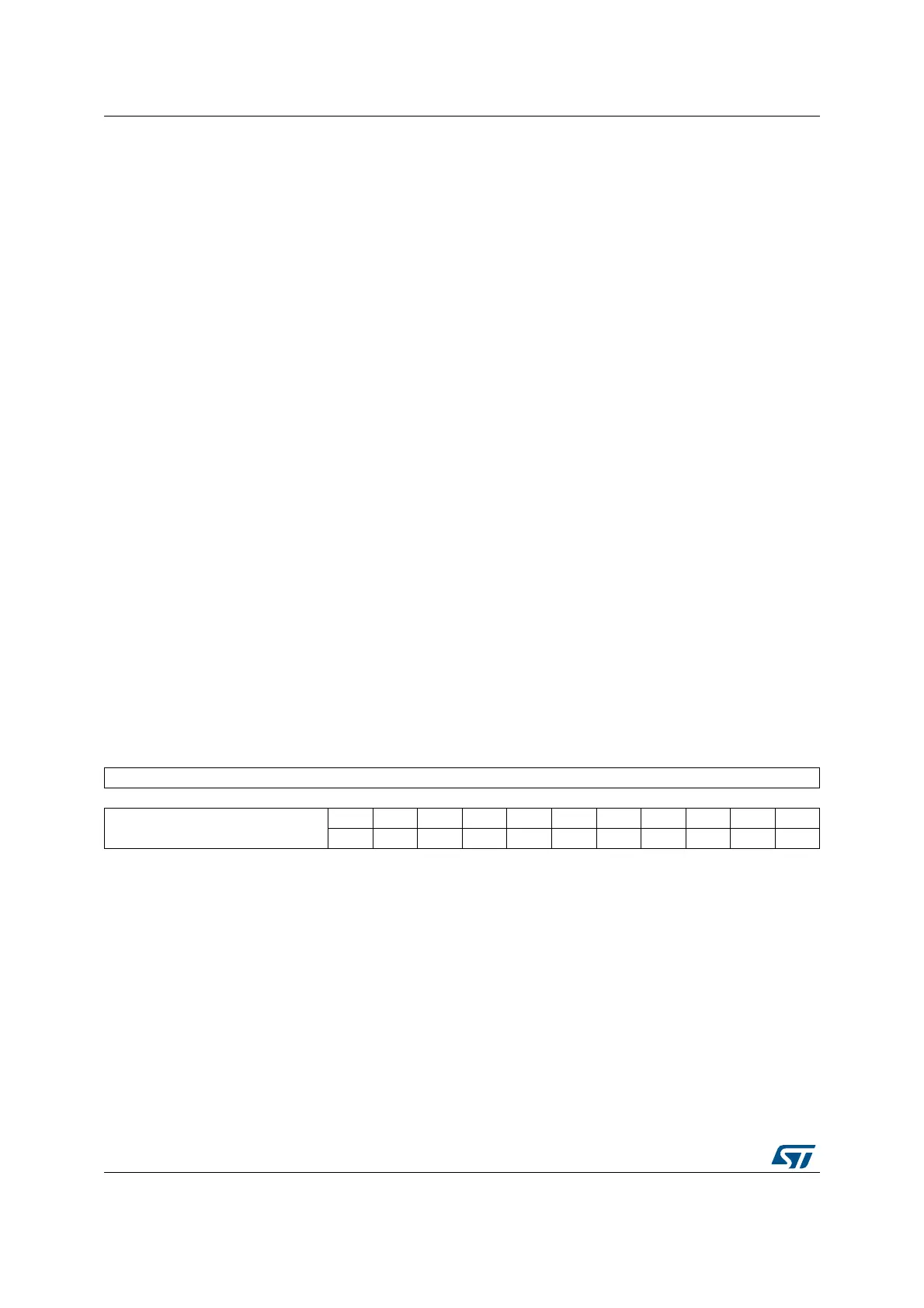

27.6.6 Control register 3 (USART_CR3)

Address offset: 0x14

Reset value: 0x0000

Bit 8 LBCL: Last bit clock pulse

This bit allows the user to select whether the clock pulse associated with the last data bit

transmitted (MSB) has to be output on the CK pin in synchronous mode.

0: The clock pulse of the last data bit is not output to the CK pin

1: The clock pulse of the last data bit is output to the CK pin

The last bit is the 8th or 9th data bit transmitted depending on the 8 or 9 bit format selected

by the M bit in the USART_CR1 register.

This bit is not available for UART4 & UART5.

Bit 7 Reserved, forced by hardware to 0.

Bit 6 LBDIE: LIN break detection interrupt enable

Break interrupt mask (break detection using break delimiter).

0: Interrupt is inhibited

1: An interrupt is generated whenever LBD=1 in the USART_SR register

Bit 5 LBDL: lin break detection length

This bit is for selection between 11 bit or 10 bit break detection.

0: 10 bit break detection

1: 11 bit break detection

Bit 4 Reserved, forced by hardware to 0.

Bits 3:0 ADD[3:0]: Address of the USART node

This bit-field gives the address of the USART node.

This is used in multiprocessor communication during mute mode, for wake up with address

mark detection.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

CTSIE CTSE RTSE DMAT DMAR SCEN NACK HDSEL IRLP IREN EIE

rw rw rw rw rw rw rw rw rw rw rw

Bits 31:11 Reserved, forced by hardware to 0.

Bit 10 CTSIE: CTS interrupt enable

0: Interrupt is inhibited

1: An interrupt is generated whenever CTS=1 in the USART_SR register

This bit is not available for UART4 & UART5.

Bit 9 CTSE: CTS enable

0: CTS hardware flow control disabled

1: CTS mode enabled, data is only transmitted when the nCTS input is asserted (tied to 0). If

the

nCTS input is deasserted while a data is being transmitted, then the transmission is

completed before stopping. If a data is written into the data register while nCTS is

deasserted, the transmission is postponed until nCTS is asserted.

This bit is not available for UART4 & UART5.

Loading...

Loading...