DocID13902 Rev 15 350/1128

RM0008 Advanced-control timers (TIM1&TIM8)

359

Note: The state of the external I/O pins connected to the complementary OCx and OCxN channels

depends on the OCx and OCxN channel state and the GPIOand AFIO registers.

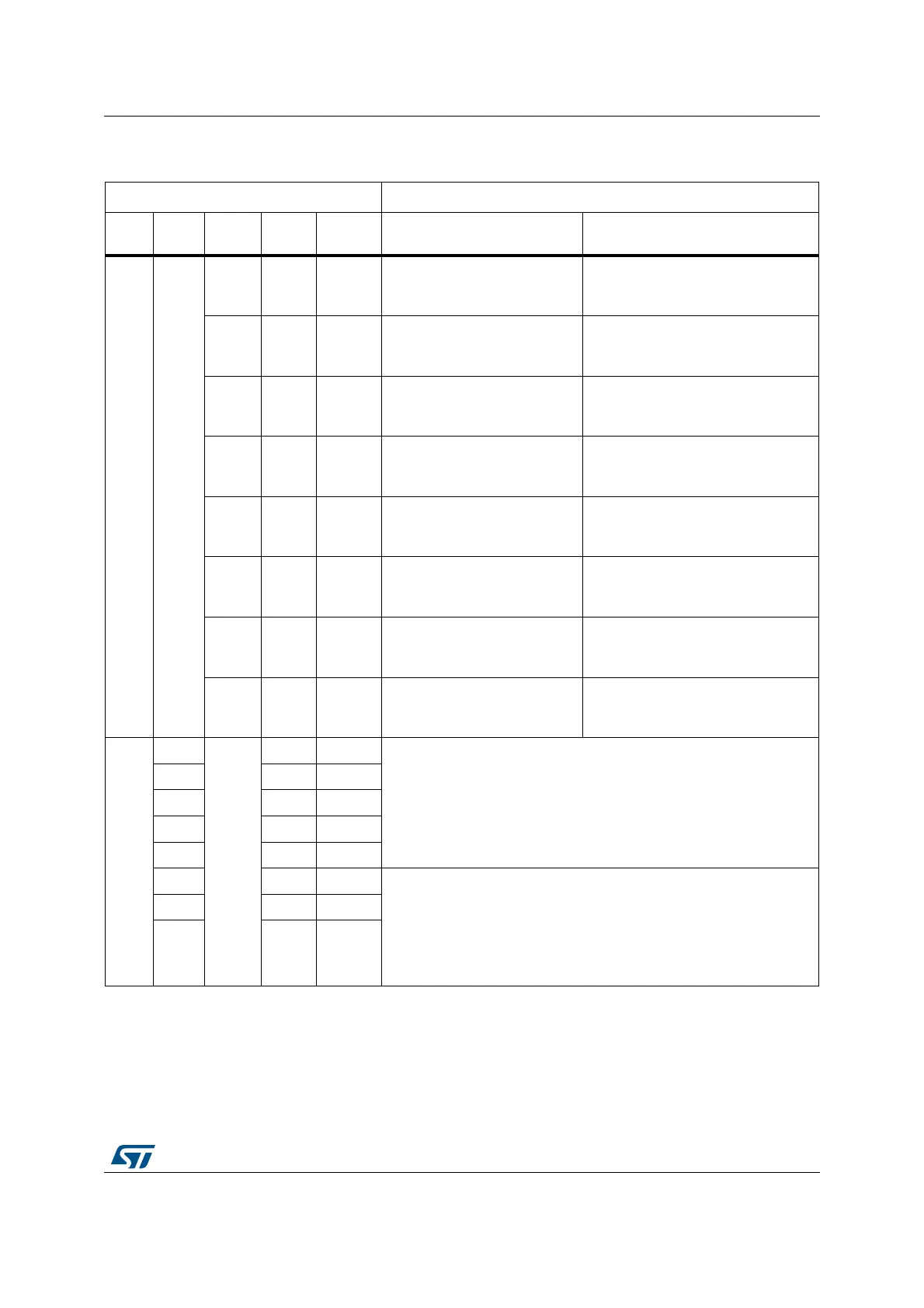

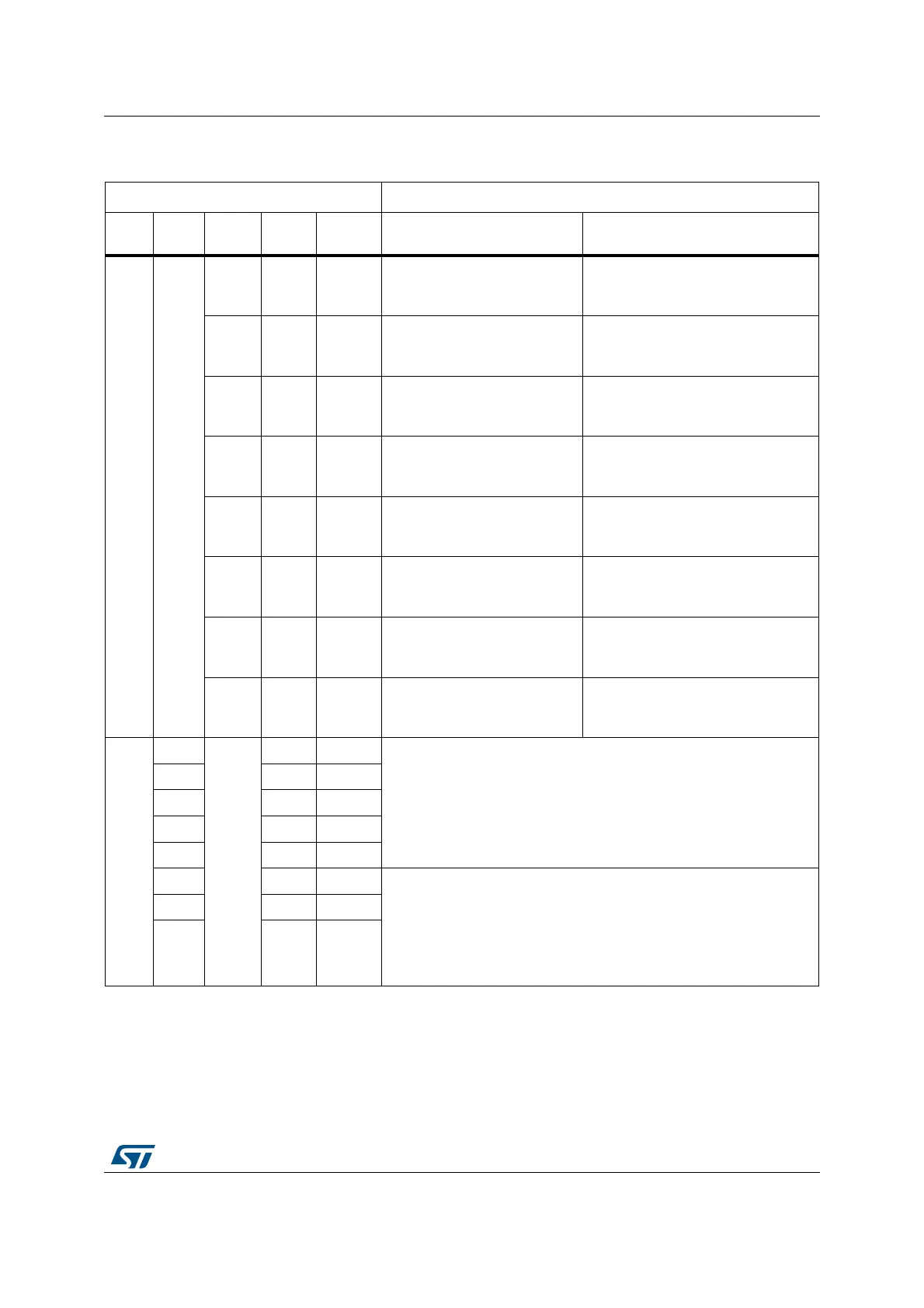

Table 83. Output control bits for complementary OCx and OCxN channels with

break feature

Control bits

Output states

(1)

MOE

bit

OSSI

bit

OSSR

bit

CCxE

bit

CCxNE

bit

OCx output state OCxN output state

1X

00 0

Output Disabled (not driven by

the timer)

OCx=0, OCx_EN=0

Output Disabled (not driven by the

timer)

OCxN=0, OCxN_EN=0

00 1

Output Disabled (not driven by

the timer)

OCx=0, OCx_EN=0

OCxREF + Polarity OCxN=OCxREF

xor CCxNP, OCxN_EN=1

01 0

OCxREF + Polarity

OCx=OCxREF xor CCxP,

OCx_EN=1

Output Disabled (not driven by the

timer)

OCxN=0, OCxN_EN=0

01 1

OCREF + Polarity + dead-time

OCx_EN=1

Complementary to OCREF (not

OCREF) + Polarity + dead-time

OCxN_EN=1

10 0

Output Disabled (not driven by

the timer)

OCx=CCxP, OCx_EN=0

Output Disabled (not driven by the

timer)

OCxN=CCxNP, OCxN_EN=0

10 1

Off-State (output enabled with

inactive state)

OCx=CCxP, OCx_EN=1

OCxREF + Polarity

OCxN=OCxREF xor CCxNP,

OCxN_EN=1

11 0

OCxREF + Polarity

OCx=OCxREF xor CCxP,

OCx_EN=1

Off-State (output enabled with

inactive state)

OCxN=CCxNP, OCxN_EN=1

11 1

OCREF + Polarity + dead-time

OCx_EN=1

Complementary to OCREF (not

OCREF) + Polarity + dead-time

OCxN_EN=1

0

0

X

00

Output Disabled (not driven by the timer)

Asynchronously: OCx=CCxP, OCx_EN=0, OCxN=CCxNP,

OCxN_EN=0

Then if the clock is present: OCx=OISx and OCxN=OISxN after a

dead-time, assuming that OISx and OISxN do not correspond to OCX

and OCxN both in active state.

001

010

011

100

1 0 1 Off-State (output enabled with inactive state)

Asynchronously: OCx=CCxP, OCx_EN=1, OCxN=CCxNP,

OCxN_EN=1

Then if the clock is present: OCx=OISx and OCxN=OISxN after a

dead-time, assuming that OISx and OISxN do not correspond to OCX

and OCxN both in active state

110

111

1. When both outputs of a channel are not used (CCxE = CCxNE = 0), the OISx, OISxN, CCxP and CCxNP bits must be kept

cleared.

Loading...

Loading...