General-purpose and alternate-function I/Os (GPIOs and AFIOs) RM0008

183/1128 DocID13902 Rev 15

9.4 AFIO registers

Refer to Section 2.1 on page 47for a list of abbreviations used in register descriptions.

Note: To read/write the AFIO_EVCR, AFIO_MAPR and AFIO_EXTICRX registers, the AFIO clock

should first be enabled. Refer to Section 7.3.7: APB2 peripheral clock enable register

(RCC_APB2ENR).

The peripheral registers have to be accessed by words (32-bit).

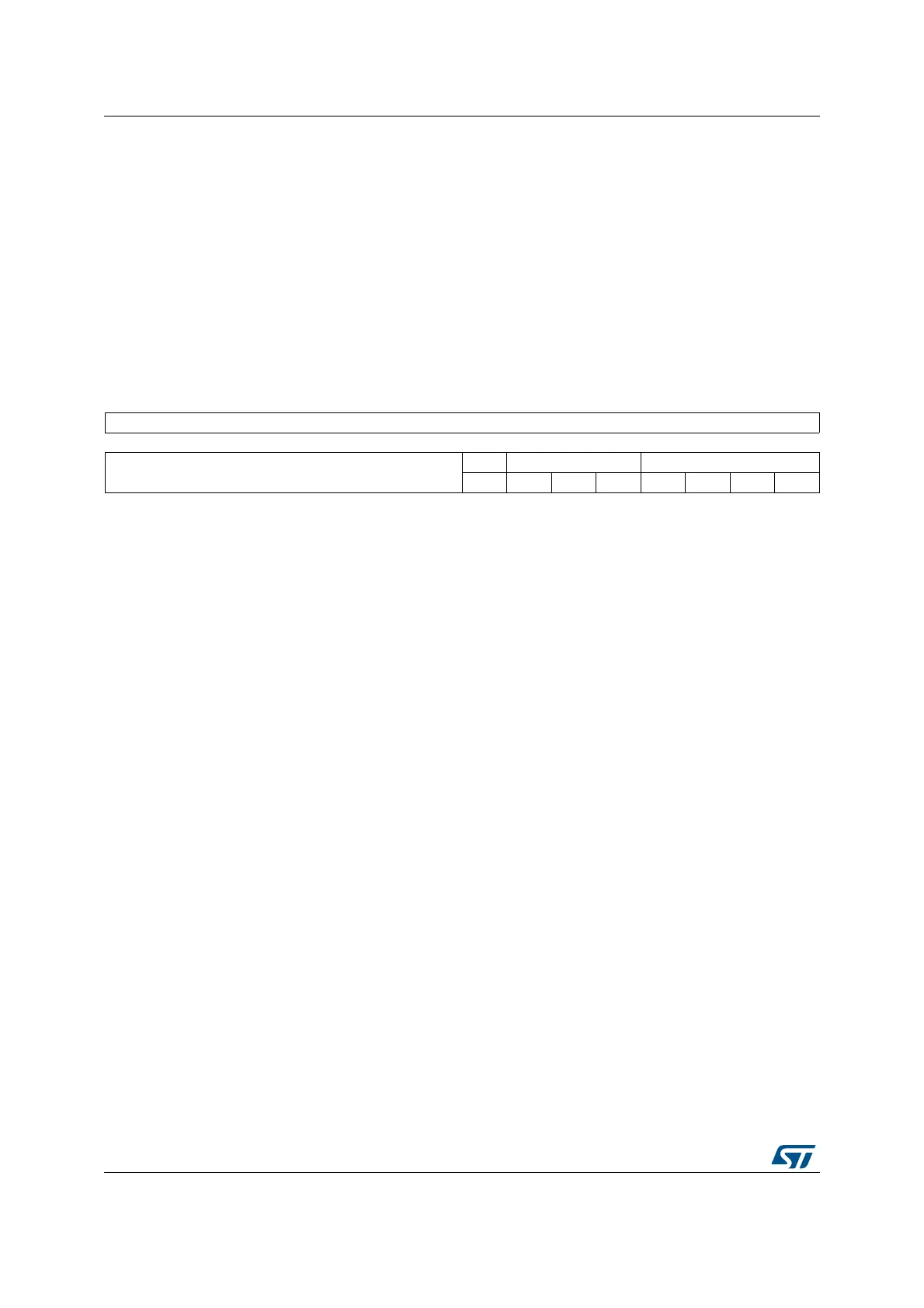

9.4.1 Event control register (AFIO_EVCR)

Address offset: 0x00

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

EVOE PORT[2:0] PIN[3:0]

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved

Bit 7 EVOE: Event output enable

Set and cleared by software. When set the EVENTOUT Cortex

®

output is connected to the

I/O selected by the PORT[2:0] and PIN[3:0] bits.

Bits 6:4 PORT[2:0]: Port selection

Set and cleared by software. Select the port used to output the Cortex

®

EVENTOUT signal.

Note: The EVENTOUT signal output capability is not extended to ports PF and PG.

000: PA selected

001: PB selected

010: PC selected

011: PD selected

100: PE selected

Bits 3:0 PIN[3:0]: Pin selection (x = A .. E)

Set and cleared by software. Select the pin used to output the Cortex

®

EVENTOUT signal.

0000: Px0 selected

0001: Px1 selected

0010: Px2 selected

0011: Px3 selected

...

1111: Px15 selected

Loading...

Loading...