General-purpose timers (TIM9 to TIM14) RM0008

457/1128 DocID13902 Rev 15

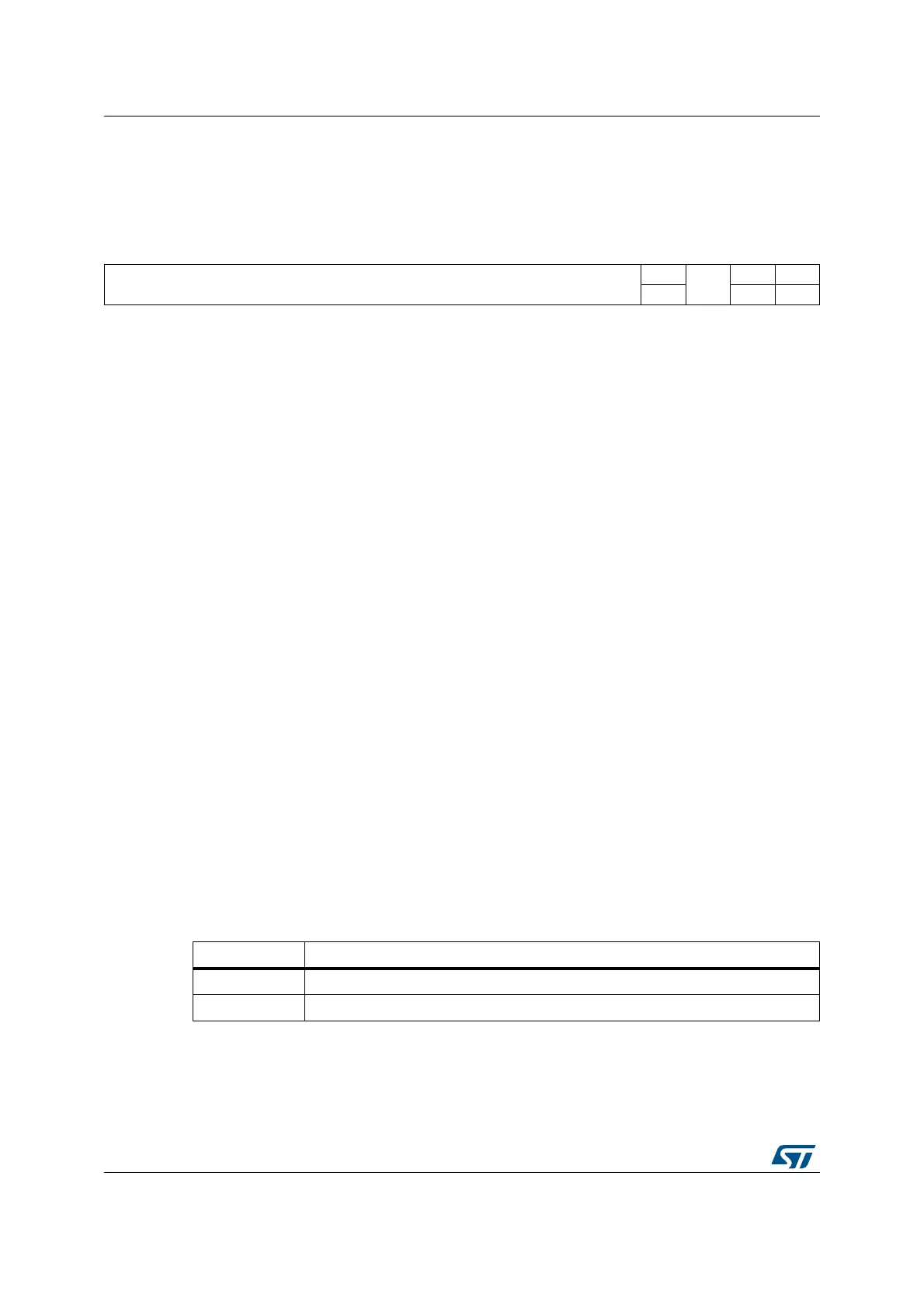

16.5.5 TIM10/11/13/14 capture/compare enable register

(TIMx_CCER)

Address offset: 0x20

Reset value: 0x0000

Note: The state of the external I/O pins connected to the standard OCx channels depends on the

OCx channel state and the GPIO registers.

1514131211109876543210

Reserved

CC1NP

Res.

CC1P CC1E

rw rw rw

Bits 15:4 Reserved, must be kept at reset value.

Bit 3 CC1NP: Capture/Compare 1 complementary output Polarity.

CC1 channel configured as output: CC1NP must be kept cleared.

CC1 channel configured as input: CC1NP bit is used in conjunction with CC1P to define

TI1FP1 polarity (refer to CC1P description).

Bit 2 Reserved, must be kept at reset value.

Bit 1 CC1P: Capture/Compare 1 output Polarity.

CC1 channel configured as output:

0: OC1 active high

1: OC1 active low

CC1 channel configured as input:

The CC1P bit selects TI1FP1 and TI2FP1 polarity for trigger or capture operations.

00: noninverted/rising edge

Circuit is sensitive to TI1FP1 rising edge (capture mode), TI1FP1 is not inverted.

01: inverted/falling edge

Circuit is sensitive to TI1FP1 falling edge (capture mode), TI1FP1 is inverted.

10: reserved, do not use this configuration.

11: noninverted/both edges

Circuit is sensitive to both TI1FP1 rising and falling edges (capture mode), TI1FP1 is not

inverted.

Bit 0 CC1E: Capture/Compare 1 output enable.

CC1 channel configured as output:

0: Off - OC1 is not active

1: On - OC1 signal is output on the corresponding output pin

CC1 channel configured as input:

This bit determines if a capture of the counter value can actually be done into the input

capture/compare register 1 (TIMx_CCR1) or not.

0: Capture disabled

1: Capture enabled

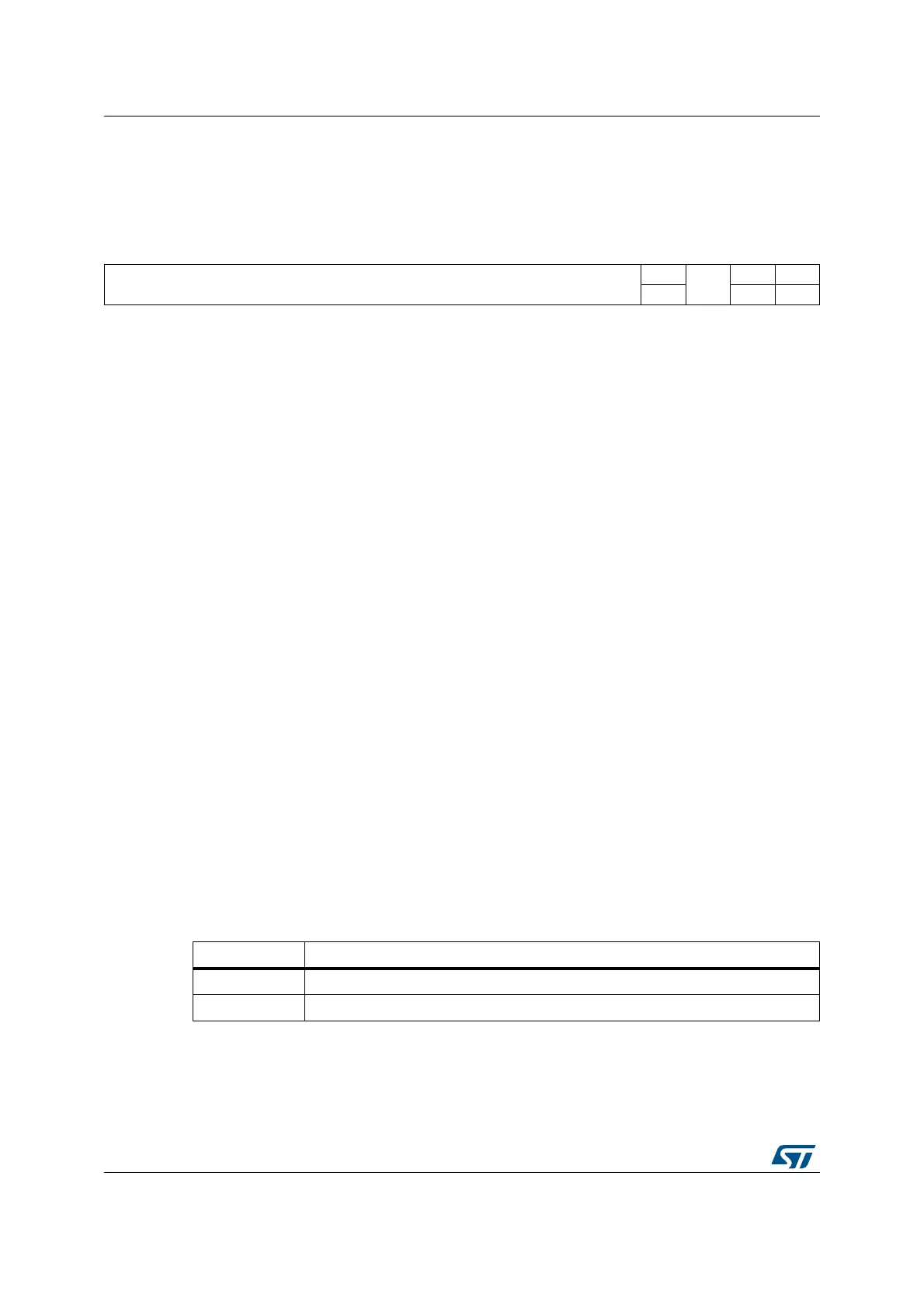

Table 92. Output control bit for standard OCx channels

CCxE bit OCx output state

0 Output Disabled (OCx=’0’, OCx_EN=’0’)

1 OCx=OCxREF + Polarity, OCx_EN=’1’

Loading...

Loading...