Flexible static memory controller (FSMC) RM0008

509/1128 DocID13902 Rev 15

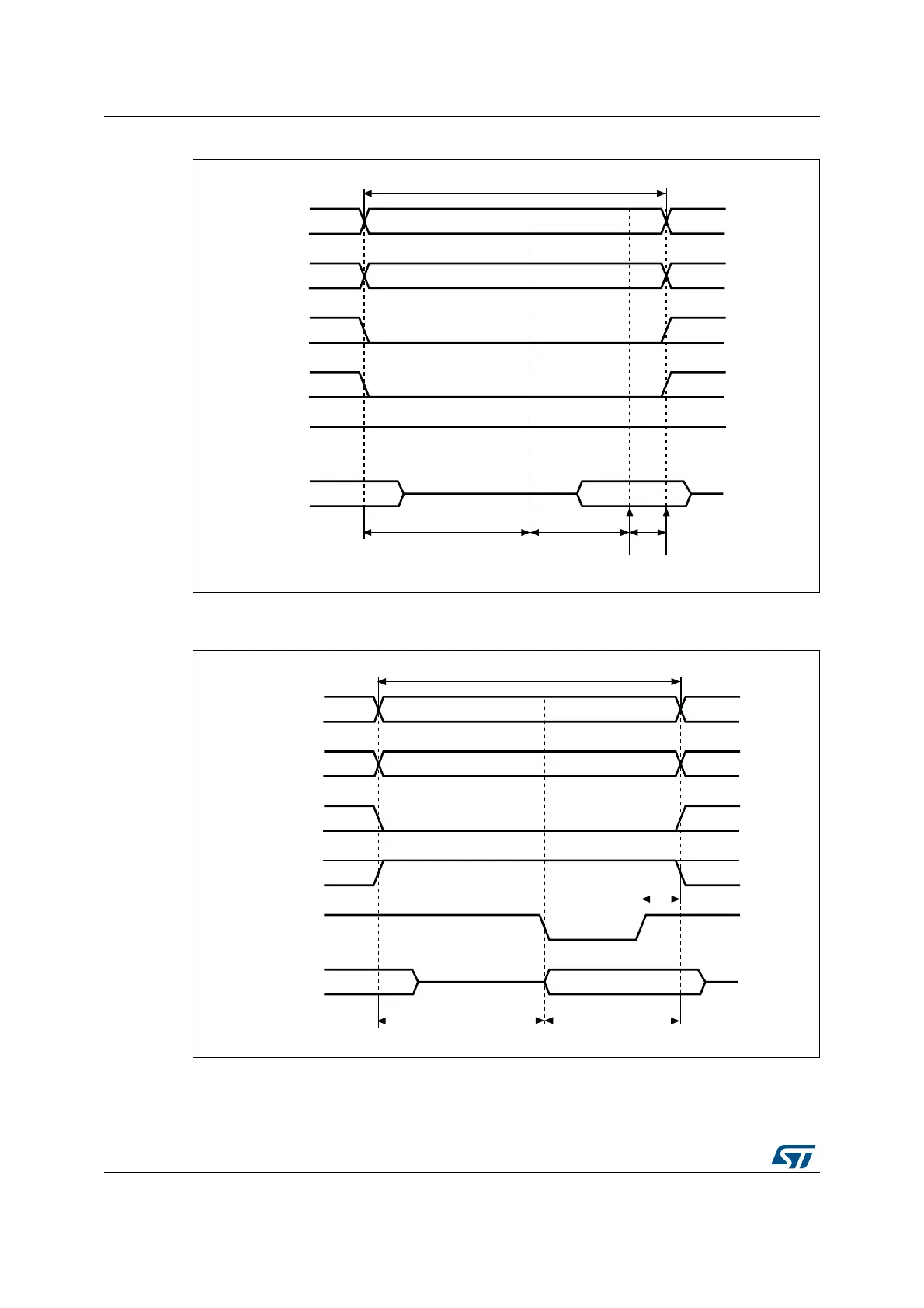

Figure 187. Mode1 read accesses

1. NBL[1:0] are driven low during read access.

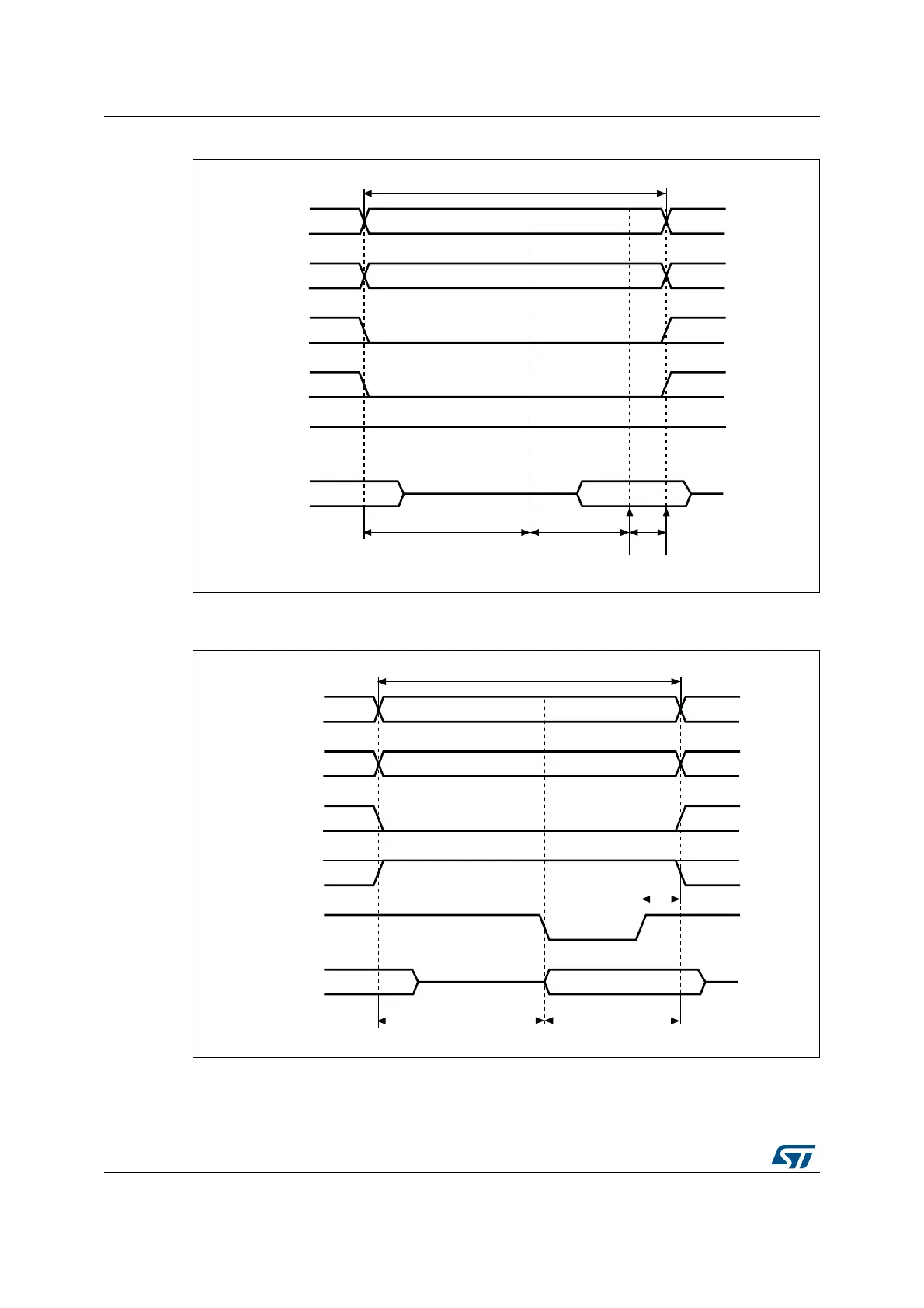

Figure 188. Mode1 write accesses

The one HCLK cycle at the end of the write transaction helps guarantee the address and

data hold time after the NWE rising edge. Due to the presence of this one HCLK cycle, the

DATAST value must be greater than zero (DATAST > 0).

A[25:0]

NOE

(ADDSET +1) (DATAST + 1)

Memory transaction

Data strobe

NEx

D[15:0]

HCLK cycles

HCLK cycles

NWE

NBL[1:0]

data driven

by memory

ai14720c

High

2 HCLK

cycles

Data sampled

A[25:0]

NOE

(ADDSET +1) (DATAST + 1)

Memory transaction

NEx

D[15:0]

HCLK cycles HCLK cycles

NWE

NBL[1:0]

data driven by FSMC

ai14721c

1HCLK

Loading...

Loading...