Low-, medium-, high- and XL-density reset and clock control (RCC) RM0008

91/1128 DocID13902 Rev 15

Low-power management reset

There are two ways to generate a low-power management reset:

1. Reset generated when entering Standby mode:

This type of reset is enabled by resetting nRST_STDBY bit in User Option Bytes. In this

case, whenever a Standby mode entry sequence is successfully executed, the device

is reset instead of entering Standby mode.

2. Reset when entering Stop mode:

This type of reset is enabled by resetting nRST_STOP bit in User Option Bytes. In this

case, whenever a Stop mode entry sequence is successfully executed, the device is

reset instead of entering Stop mode.

For further information on the User Option Bytes, refer to the STM32F10xxx Flash

programming manual.

7.1.2 Power reset

A power reset is generated when one of the following events occurs:

1. Power-on/power-down reset (POR/PDR reset)

2. When exiting Standby mode

A power reset sets all registers to their reset values except the Backup domain (see

Figure 4)

These sources act on the NRST pin and it is always kept low during the delay phase. The

RESET service routine vector is fixed at address

0x0000_0004 in the memory map.

The system reset signal provided to the device is output on the NRST pin. The pulse

generator guarantees a minimum reset pulse duration of 20 µs for each reset source

(external or internal reset). In case of an external reset, the reset pulse is generated while

the NRST pin is asserted low.

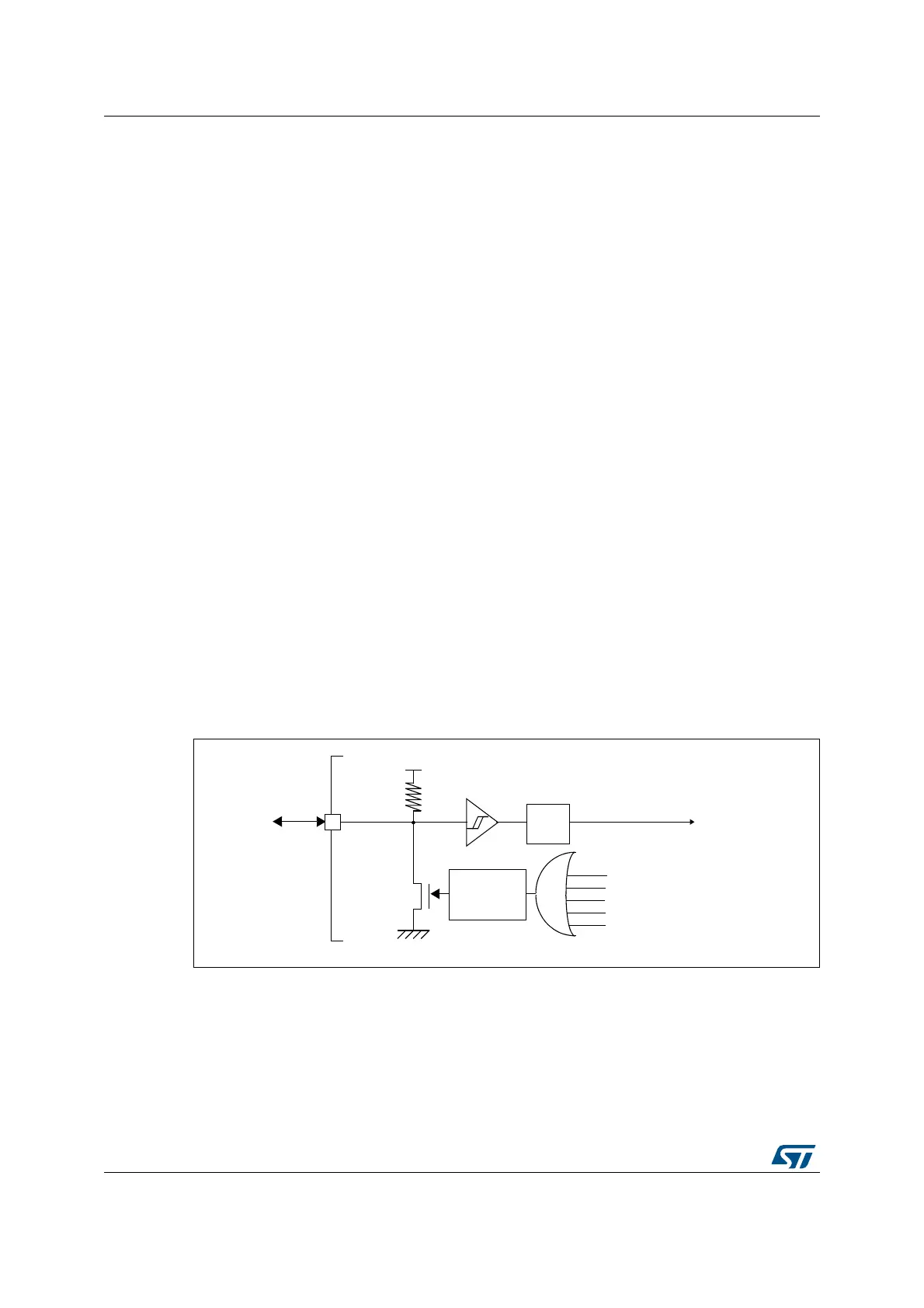

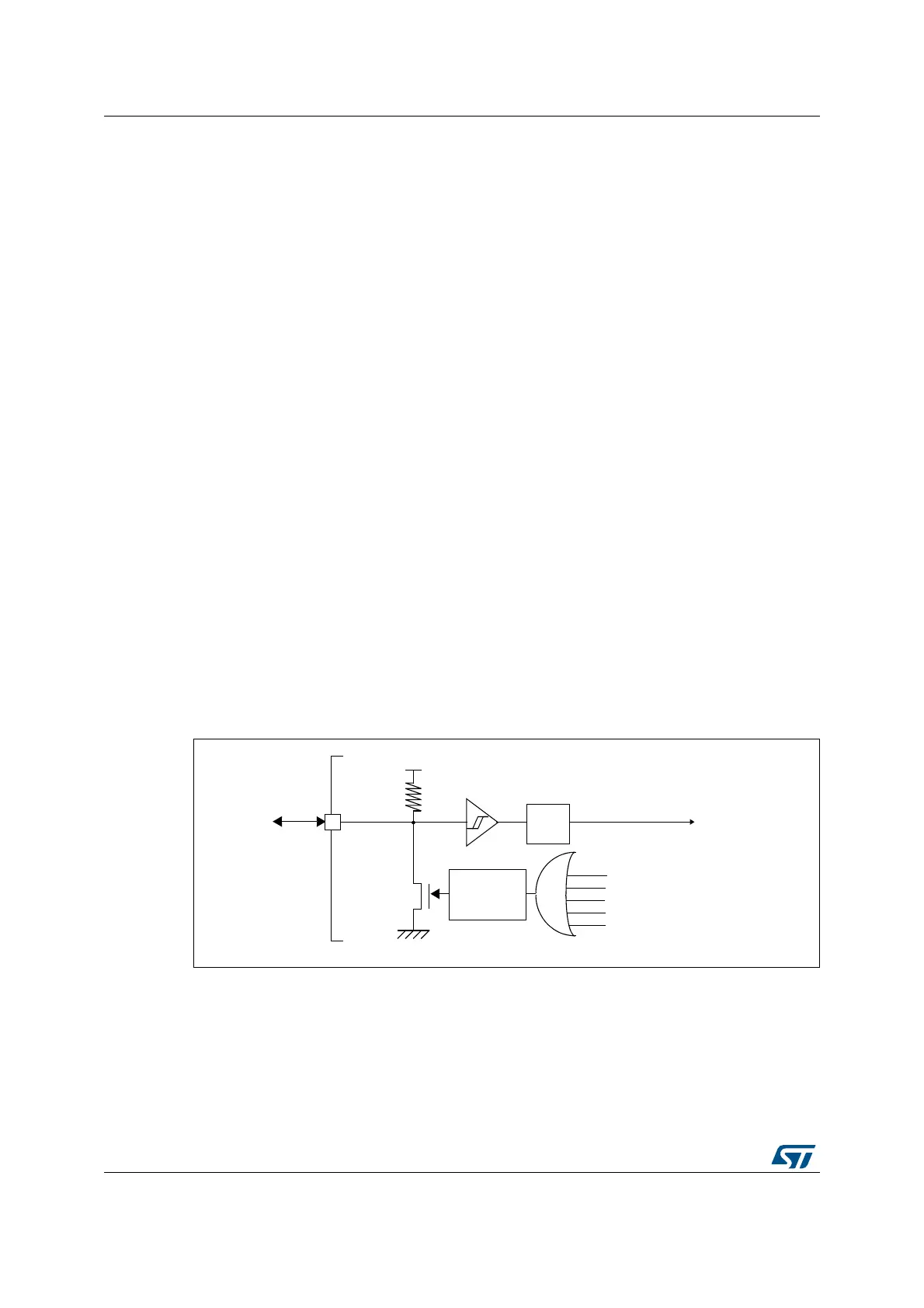

Figure 7. Simplified diagram of the reset circuit

1567

5

38

9

''

9

''$

::'*UHVHW

,:'*UHVHW

3XOVH

JHQHUDWRU

3RZHUUHVHW

([WHUQDO

UHVHW

PLQV

6\VWHPUHVHW

)LOWHU

6RIWZDUHUHVHW

/RZSRZHUPDQDJHPHQWUHVHW

DLF

Loading...

Loading...