DocID13902 Rev 15 500/1128

RM0008 Flexible static memory controller (FSMC)

555

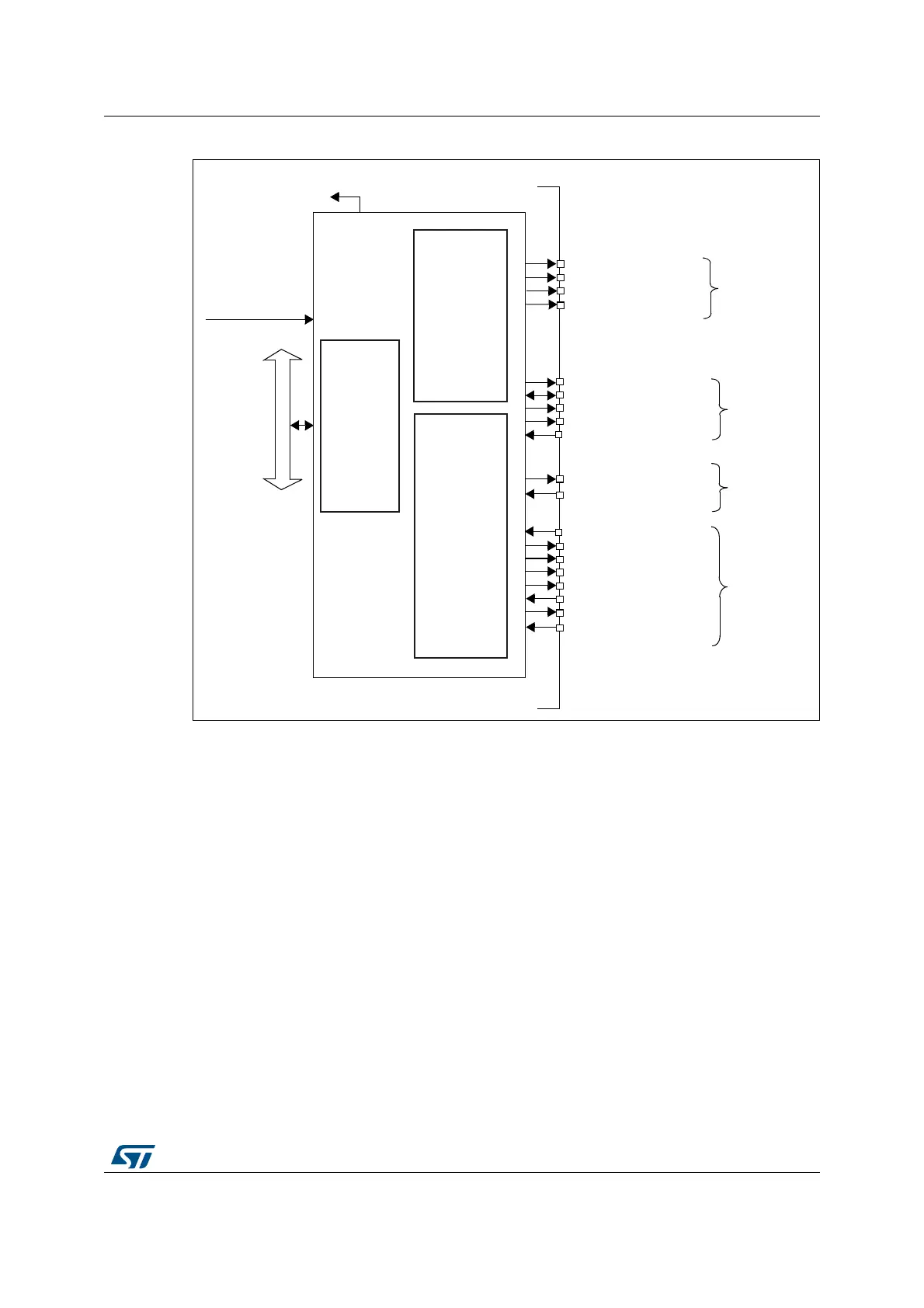

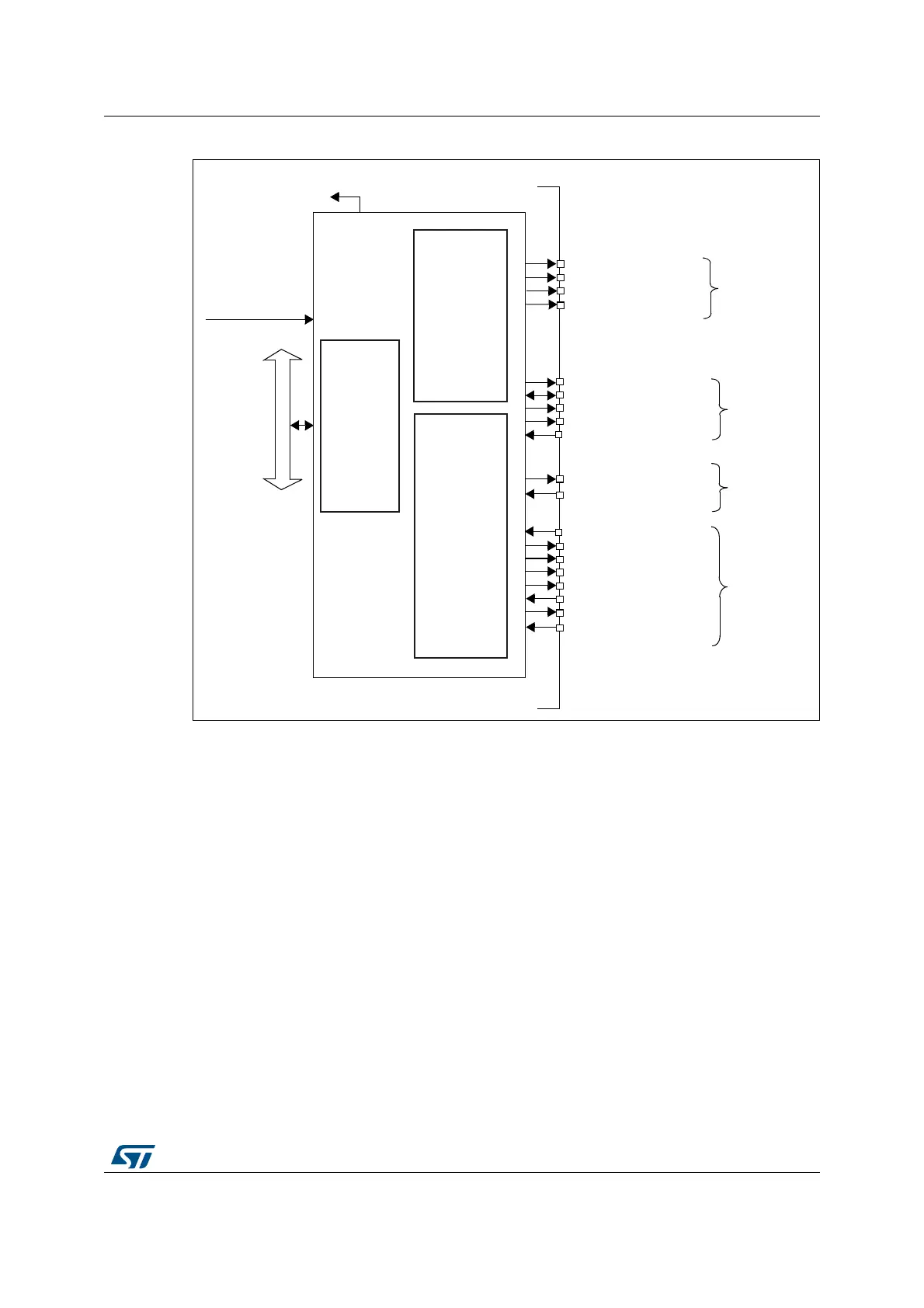

Figure 185. FSMC block diagram

21.3 AHB interface

The AHB slave interface enables internal CPUs and other bus master peripherals to access

the external static memories.

AHB transactions are translated into the external device protocol. In particular, if the

selected external memory is 16 or 8 bits wide, 32-bit wide transactions on the AHB are split

into consecutive 16- or 8-bit accesses. The Chip Select is kept low or toggles between the

consecutive accesses when perfoming 32-bit aligned or 32-bit unaligned accesses

respectively.

The FSMC generates an AHB error in the following conditions:

• When reading or writing to an FSMC bank which is not enabled

• When reading or writing to the NOR Flash bank while the FACCEN bit is reset in the

FSMC_BCRx register.

• When reading or writing to the PC Card banks while the input pin FSMC_CD (Card

Presence Detection) is low.

(#,+

SIGNALS

.!.$

SIGNALS

./2032!-

&3-#?.%;=

&3-#?.,OR.!$6

&3-#?.7!)4

&3-#?./%

&3-#?.7%

&3-#?.)/2$

&3-#?.2%'

&3-#?#$

SIGNALS

0##ARD

AID

&3-#?.",;=

&3-#?.#%;=

&3-#?).4;=

&3-#?).42

&3-#?.#%?

&3-#?.#%?

&3-#?.)/72

&3-#?.)/3

&3-#?#,+

&3-#INTERRUPTTO.6)#

&ROMCLOCK

CONTROLLER

!("BUS

#ONFIGURATION

REGISTERS

./2032!-

MEMORY

CONTROLLER

.!.$0##ARD

MEMORY

CONTROLLER

&3-#?!;=

&3-#?$;=

3HARED

SIGNALS

Loading...

Loading...