DocID13902 Rev 15 516/1128

RM0008 Flexible static memory controller (FSMC)

555

Note: The FSMC_BWTRx register is valid only if extended mode is set (mode B), otherwise all its

content is don’t care.

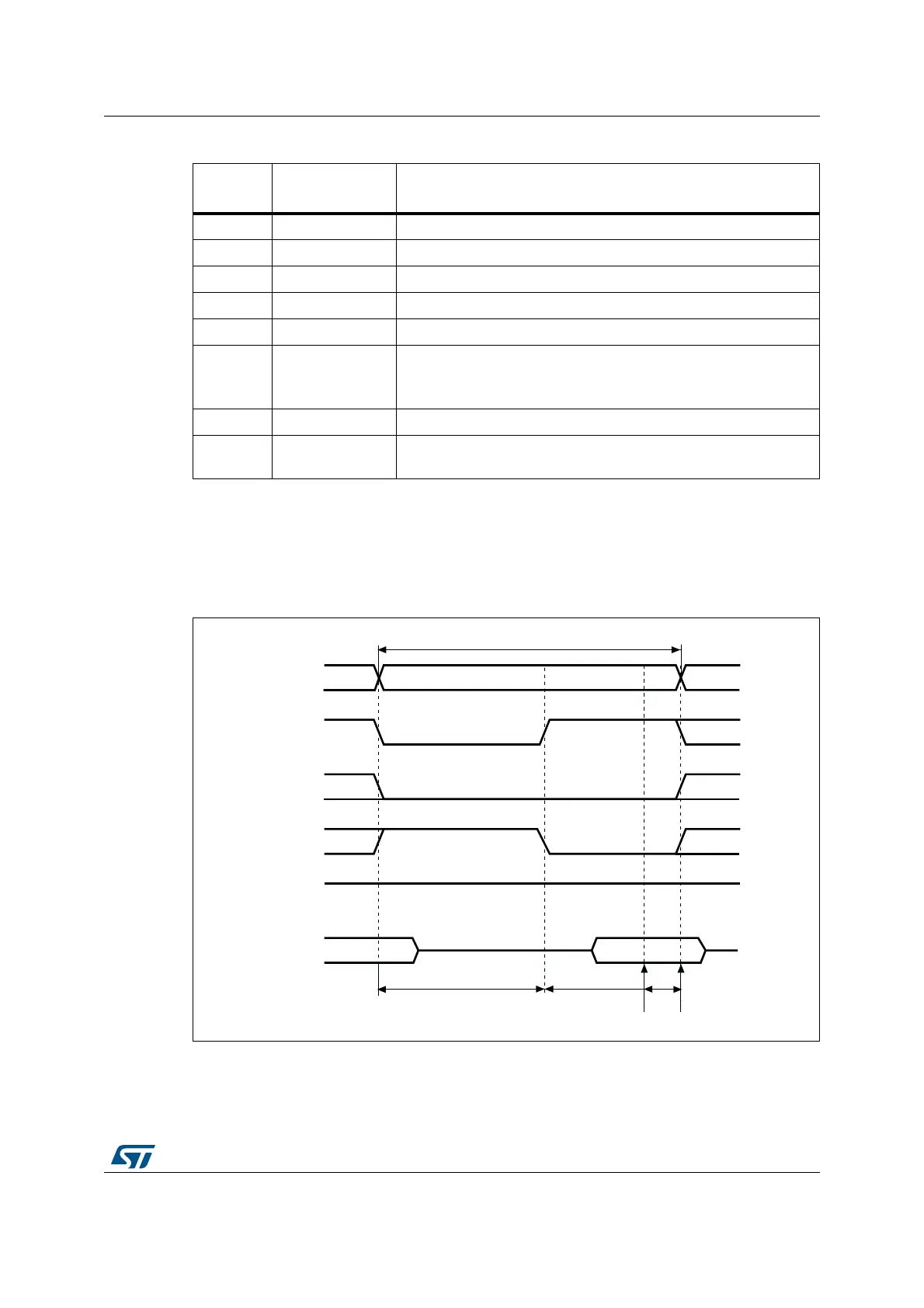

Mode C - NOR Flash - OE toggling

Figure 194. Mode C read accesses

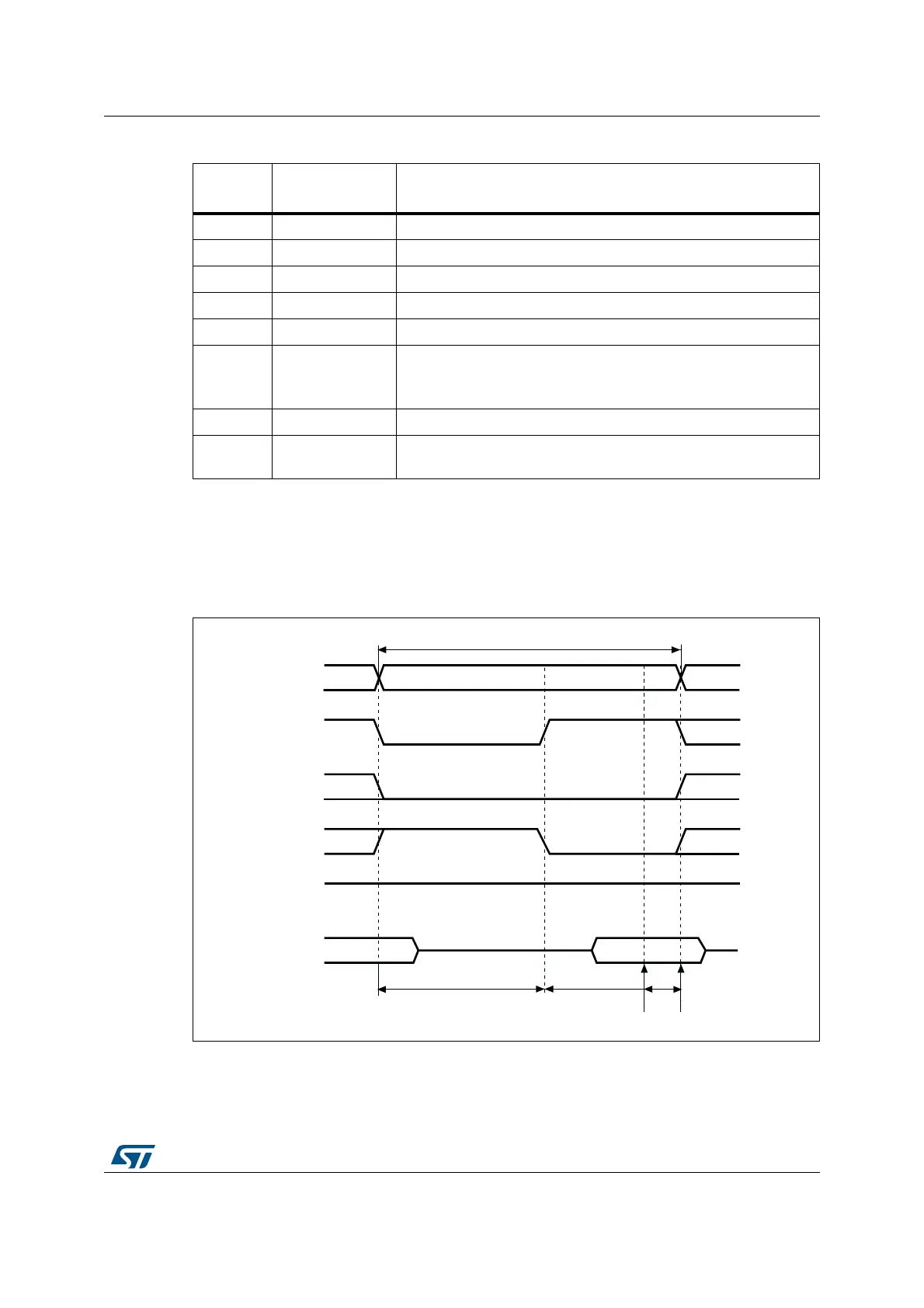

Table 116. FSMC_BWTRx bit fields

Bit

number

Bit name Value to set

31:30 Reserved 0x0

29-28 ACCMOD 0x1

27-24 DATLAT Don’t care

23-20 CLKDIV Don’t care

19-16 BUSTURN Time between NEx high to NEx low (BUSTURN HCLK)

15-8 DATAST

Duration of the second access phase (DATAST+1 HCLK cycles for

write accesses, DATAST+3 HCLK cycles for write accesses).

This value cannot be 0 (minimum is 1).

7-4 ADDHLD Don’t care

3-0 ADDSET

Duration of the first access phase (ADDSET+1 HCLK cycles) for

write accesses.

A[25:0]

NOE

(ADDSET +1) (DATAST + 1)

Memory transaction

Data strobe

NEx

D[15:0]

HCLK cycles HCLK cycles

NWE

NADV

data driven

by memory

ai14725c

High

2 HCLK

cycles

Data sampled

Loading...

Loading...