Debug support (DBG) RM0008

1069/1128 DocID13902 Rev 15

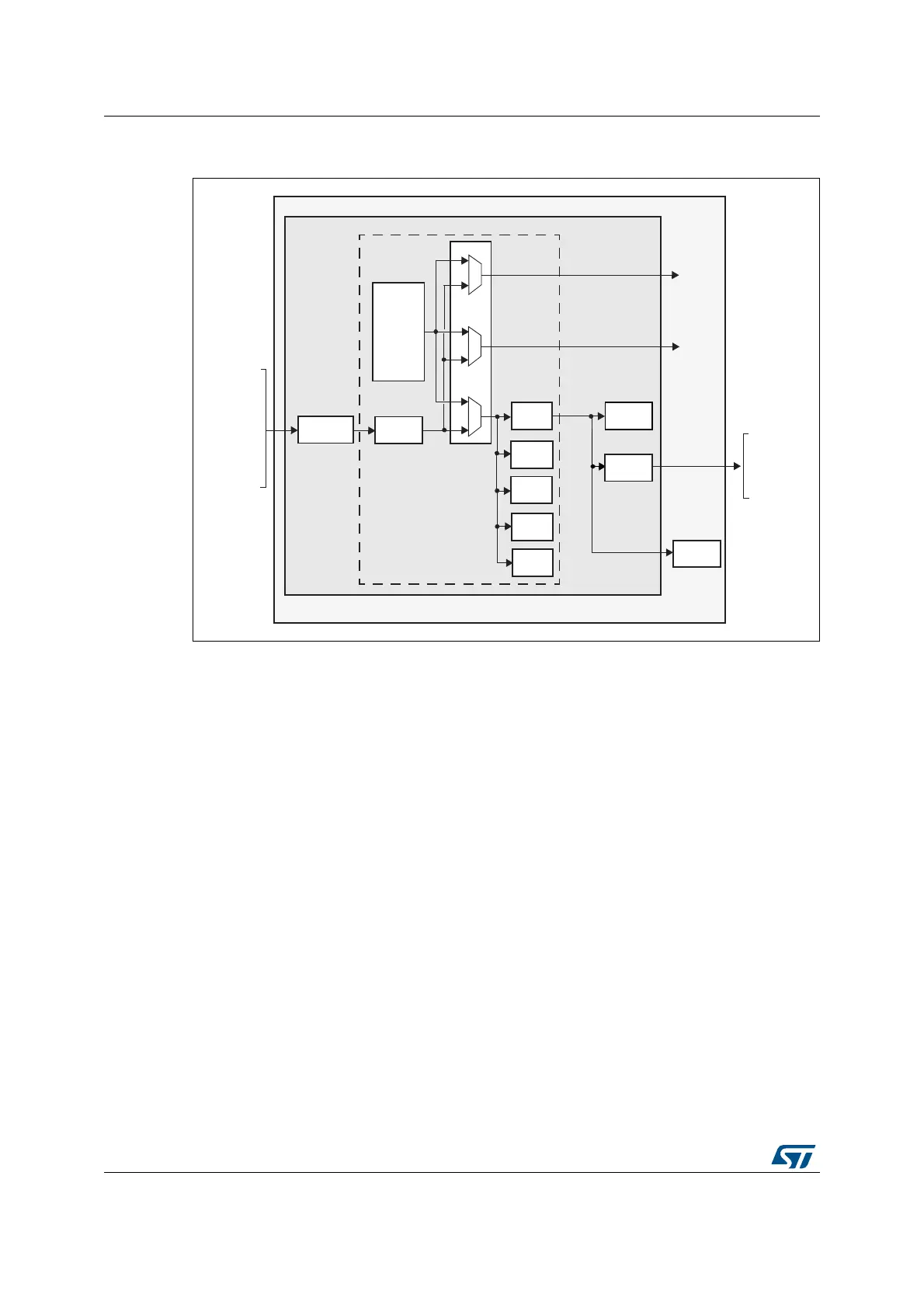

Figure 360. Block diagram of STM32 MCU and Cortex

®

-M3-level

debug support

Note: The debug features embedded in the Cortex

®

-M3 core are a subset of the ARM

®

CoreSight

Design Kit.

The ARM

®

Cortex

®

-M3 core provides integrated on-chip debug support. It is comprised of:

• SWJ-DP: Serial wire / JTAG debug port

• AHP-AP: AHB access

port

• ITM: Instrumentation trace macrocell

• FPB: Flash patch breakpoint

• DWT: Data watchpoint trigger

• TPUI: Trace port unit interface (available on larger packages, where the corresponding

pins are mapped)

• ETM: Embedded Trace Macrocell (available on larger packages, where the

corresponding pins are mapped)

It also includes debug features dedicated to the STM32F10xxx:

• Flexible debug pinout assignment

• MCU debug box (support for low-power modes, control over peripheral clocks, etc.)

Note: For further information on debug functionality supported by the ARM

®

Cortex

®

-M3 core,

refer to the Cortex

®

-M3-r1p1 Technical Reference Manual and to the CoreSight Design Kit-

r1p0 TRM (see Section 31.2: Reference ARM® documentation).

Cortex-M3

Core

SWJ-DP

AHB-AP

Bridge

NVIC

DWT

FPB

ITM

ETM

DCode

interface

System

interface

Internal private

peripheral bus (PPB)

External private

peripheral bus (PPB)

Bus matrix

Data

Trace port

DBGMCU

STM32 MCU debug support

Cortex-M3 debug support

JTMS/

JTDI

JTDO/

NJTRST

JTCK/

SWDIO

SWCLK

TRACESWO

TRACESWO

TRACECK

TRACED[3:0]

TPIU

ai17138

Loading...

Loading...