Spartan-6 FPGA PCB Design and Pin Planning www.xilinx.com 23

UG393 (v1.1) April 29, 2010

Basic PDS Principles

Requirements for choosing decoupling capacitors:

• For a specific capacitance value, choose the smallest package available.

- or -

• For a specific package size (essentially a fixed inductance value), choose the highest

capacitance value available in that package.

Surface-mount chip capacitors are the smallest capacitors available and are a good choice

for discrete decoupling capacitors:

• For values from 100 µF to very small values such as 0.01 µF, X7R or X5R type

capacitors are usually used. These capacitors have a low parasitic inductance and a

low ESR, with an acceptable temperature characteristic.

• For larger values, such as 100 µF to 1000 µF, tantalum capacitors are used. These

capacitors have a low parasitic inductance and a medium ESR, giving them a low Q

factor and consequently a very wide range of effective frequencies.

If tantalum capacitors are not available or cannot be used, low-ESR, low-inductance

electrolytic capacitors can be used, provided they have comparable ESR and ESL values.

Other new technologies with similar characteristics are also available (Os-Con, POSCAP,

and Polymer-Electrolytic SMT).

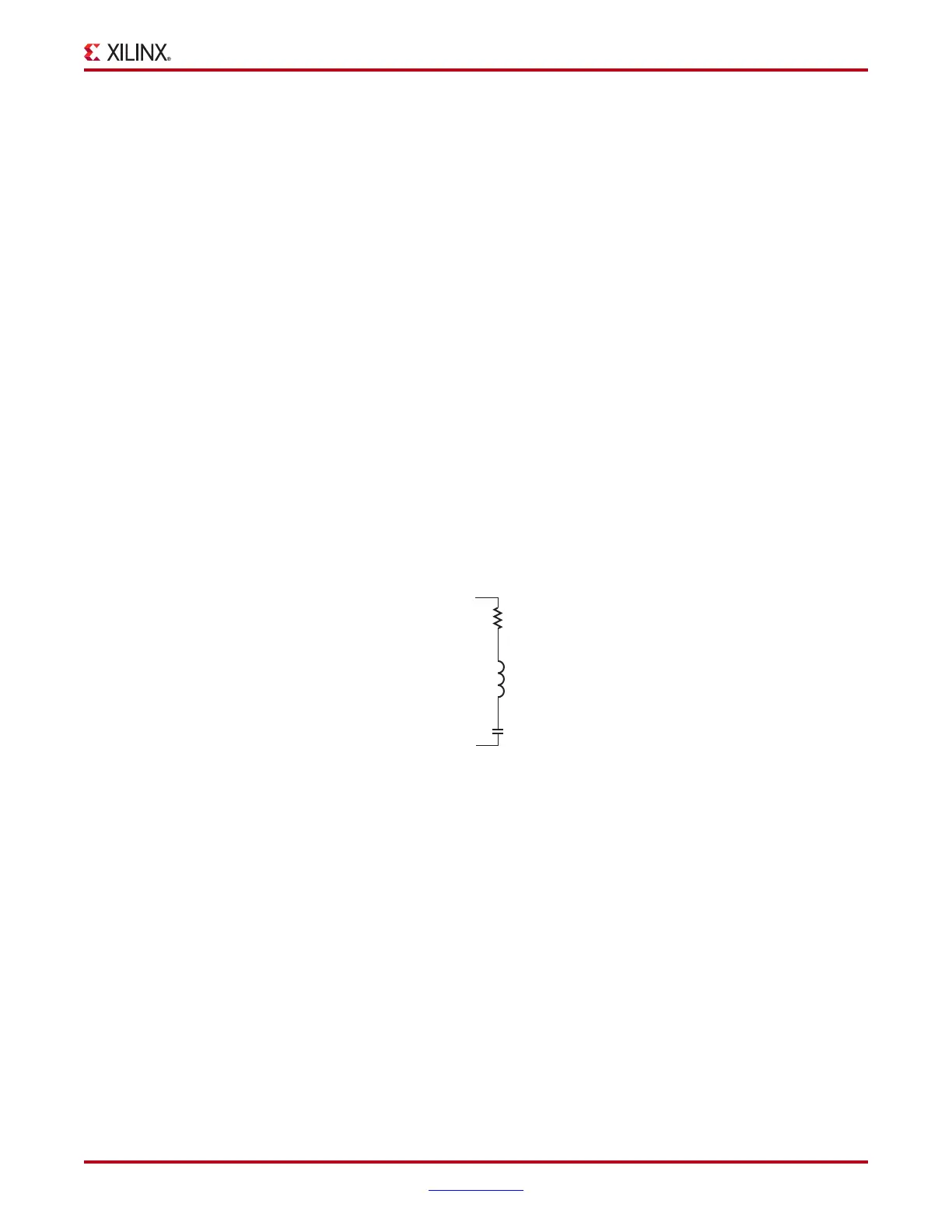

A real capacitor of any type then not only has capacitance characteristics but also

inductance and resistance characteristics. Figure 2-5 shows the parasitic model of a real

capacitor. A real capacitor should be treated as an RLC circuit (a circuit consisting of a

resistor (R), an inductor (L), and a capacitor (C), connected in series).

Figure 2-6 shows a real capacitor’s impedance characteristic. Overlaid on this plot are

dashed-line curves corresponding to the capacitor’s capacitance and parasitic inductance

(ESL). These two curves combine to form the RLC circuit’s total impedance characteristic,

softened or sharpened by the capacitor’s ESR.

X-Ref Target - Figure 2-5

Figure 2-5: Parasitics of a Real, Non-Ideal Capacitor

C

ESL

ESR

ug393_c2_05_091809

Loading...

Loading...