50 www.xilinx.com Spartan-6 FPGA PCB Design and Pin Planning

UG393 (v1.1) April 29, 2010

Chapter 5: Design of Transitions for High-Speed Signals

The 2D field-solver example shows that close to 50Ω can be achieved if the ground plane

under the pad footprint is cleared out. A 3D field solver is then used to verify this result to

a greater degree of accuracy.

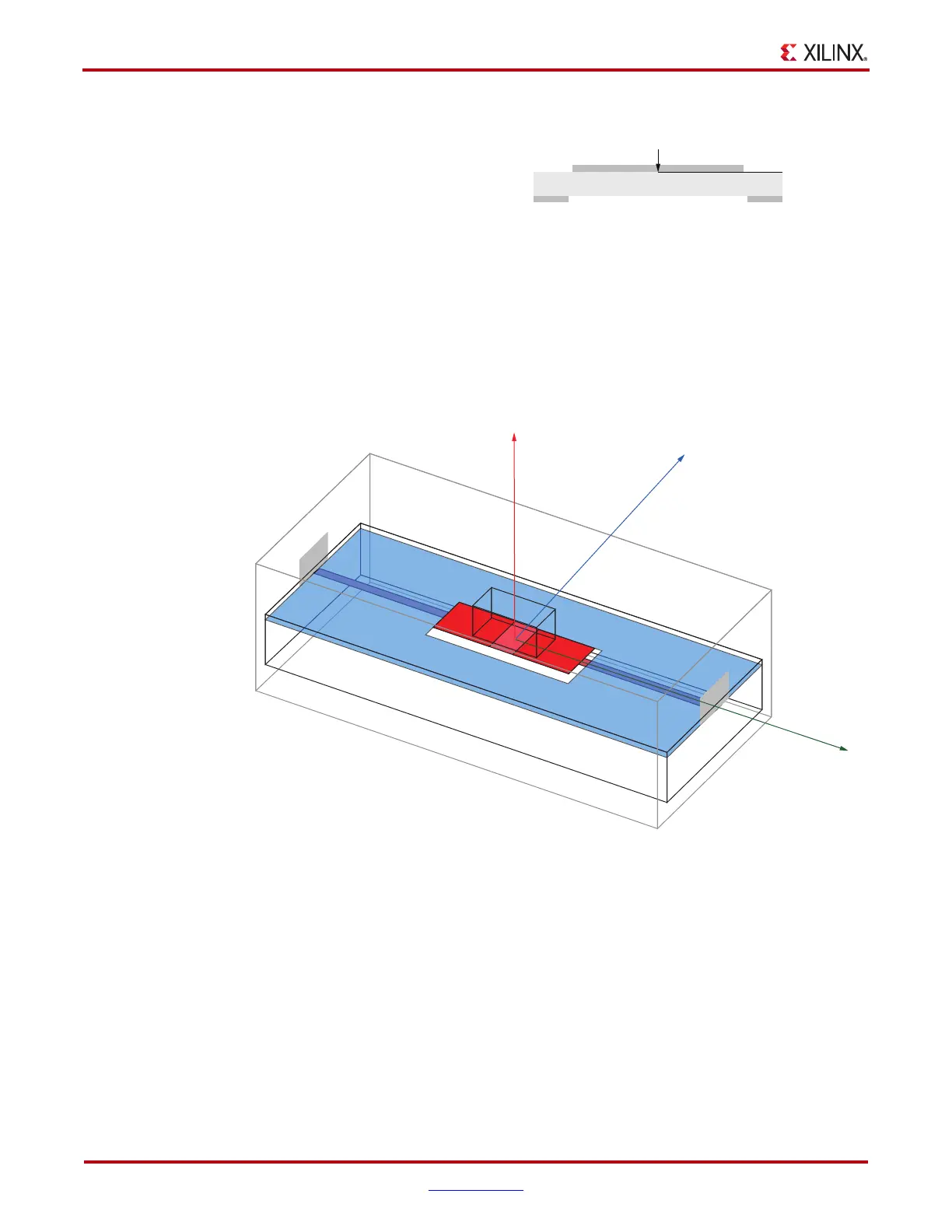

Figure 5-6 shows the ground plane cleared away exactly as it was for the 2D simulation.

Using frequency domain analysis within HFSS, there is a 20 dB (10x) improvement in

return loss using this technique.

Figure 5-7 shows the return loss comparison between 0402 pad structures with linear scale.

X-Ref Target - Figure 5-5

Figure 5-5: Transition Optimization

X-Ref Target - Figure 5-6

Figure 5-6: Ansoft HFSS Model of Pad Clear-Out

- L = 241 nH/m

- C = 89 pF/m

- Zo = 52Ω

28 Mil Pad

UG393_c5_05_091809

Loading...

Loading...