98 HB700 | CPU | PMC921xEx | en | 24-04

Deployment CPU iC921xM-EC

Reset to factory settings

type 2

Start-Up in Safe Mode

4. Switch off the power supply of the CPU.

5. Set the DIP switch S1 to the default position:

S1 S1-1 S1-2 Action

OFF OFF After PowerON the CPU starts in Standard

Mode

- Default setting.

6. Switch on the power supply of the CPU again.

🡆 The CPU starts in Standard Mode.

■ The overlay file system with user program, configurations, user data and firmware

adjustments is deleted.

■ The non-volatile memory for retentive data is deleted.

■ The current firmware version is overwritten by the original firmware version and the

delivery state of the CPU is restored.

1. Switch off the power supply of the CPU.

2. Press and hold the operating mode switch in position MR and switch on the power

supply of the CPU again.

3. As soon as the LEDs show the following behavior after start-up, release the oper-

ating mode switch again (duration ca. 30s):

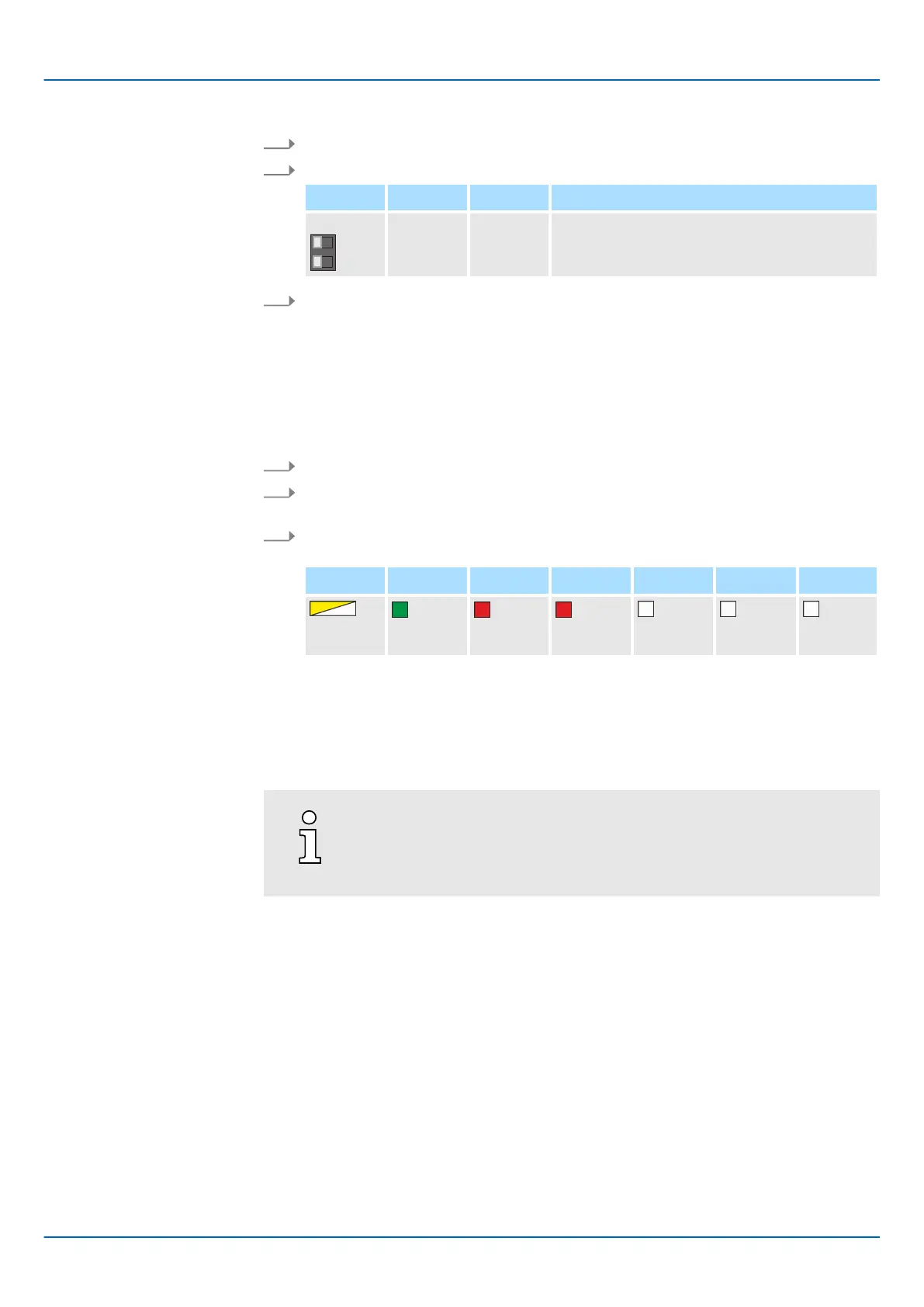

Status RN ER IO ER PN-C ER PN-D ER IO DIAG

yellow

2Hz

green red red

🡆 The CPU now executes a reset to factory setting type 2 and is then in the

delivery state.

4.8 Firmware update

Y

ou can update the firmware via the Web-based management WBM. ⮫‘Firmware

Update’...page 207

Please note that you can only execute a firmware update with adminis-

trator rights!

4.9 Safe Mode

By means of the DIP switch ‘S1’

beneath the front flap you can start your CPU in Safe

Mode. Here the CPU starts with the following behavior:

■ The CPU goes to RUN with the default project.

■ A project can be loaded but not executed.

■ The SliceBus is switched off.

■ All field buses are disabled.

■ The parametrization memory with the current firmware version and the overlay file

system

remains unchanged.

■ During online access, you are informed that the CPU is in Safe Mode.

■ The non-volatile memory for retentive data remains unchanged.

■ The CPU can only be reached via the default IP address.

■ Additionally, a memory area reserved exclusively for Safe Mode is enabled, which

allows the CPU to restart in the event of a memory overflow

.

Loading...

Loading...