101

ABOV Semiconductor Co., Ltd.

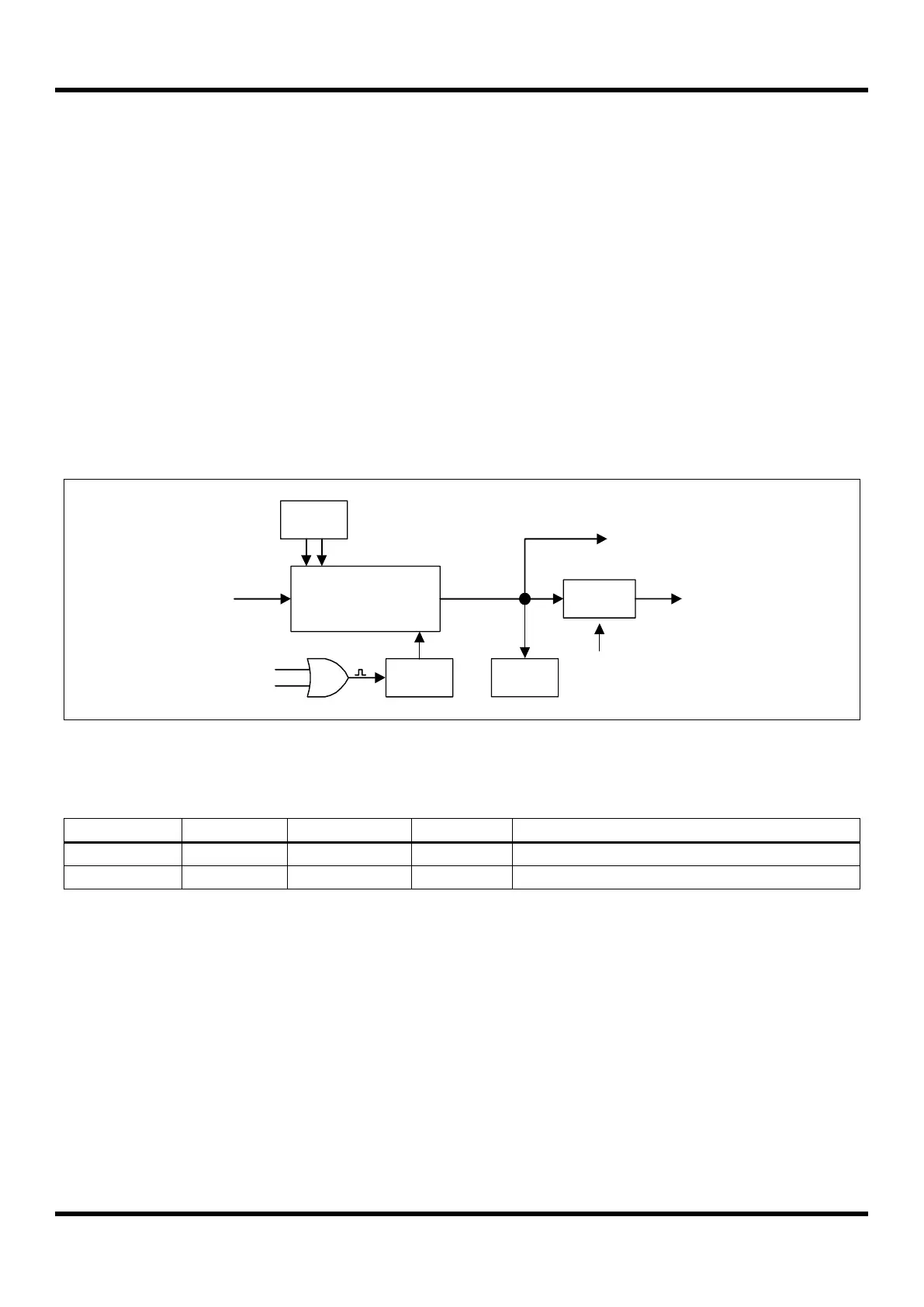

11.2 Basic Interval Timer

11.2.1 Overview

The MC96F6432S has one 8-bit basic interval timer that is free-run and can’t stop. Block diagram is shown in Figure

11.2. In addition, the basic interval timer generates the time base for watchdog timer counting. It also provides a basic

interval timer interrupt (BITIFR).

The MC96F6432S has these basic interval timer (BIT) features:

− During Power On, BIT gives a stable clock generation time

− On exiting Stop mode, BIT gives a stable clock generation time

− As timer function, timer interrupt occurrence

11.2.2 Block Diagram

BIT Clock

BCK[2:0]

8-Bit Up Counter

BITCNT

BCLR

clear

BITIFR

To interrupt

block

selected bit

overflow

WDT

INT_ACK

clear

Start CPU

RESET

STOP

Figure 11.2 Basic Interval Timer Block Diagram

11.2.3 Register Map

Basic Interval Timer Counter Register

Basic Interval Timer Control Register

Table 11.2 Basic Interval Timer Register Map

Loading...

Loading...