208

ABOV Semiconductor Co., Ltd.

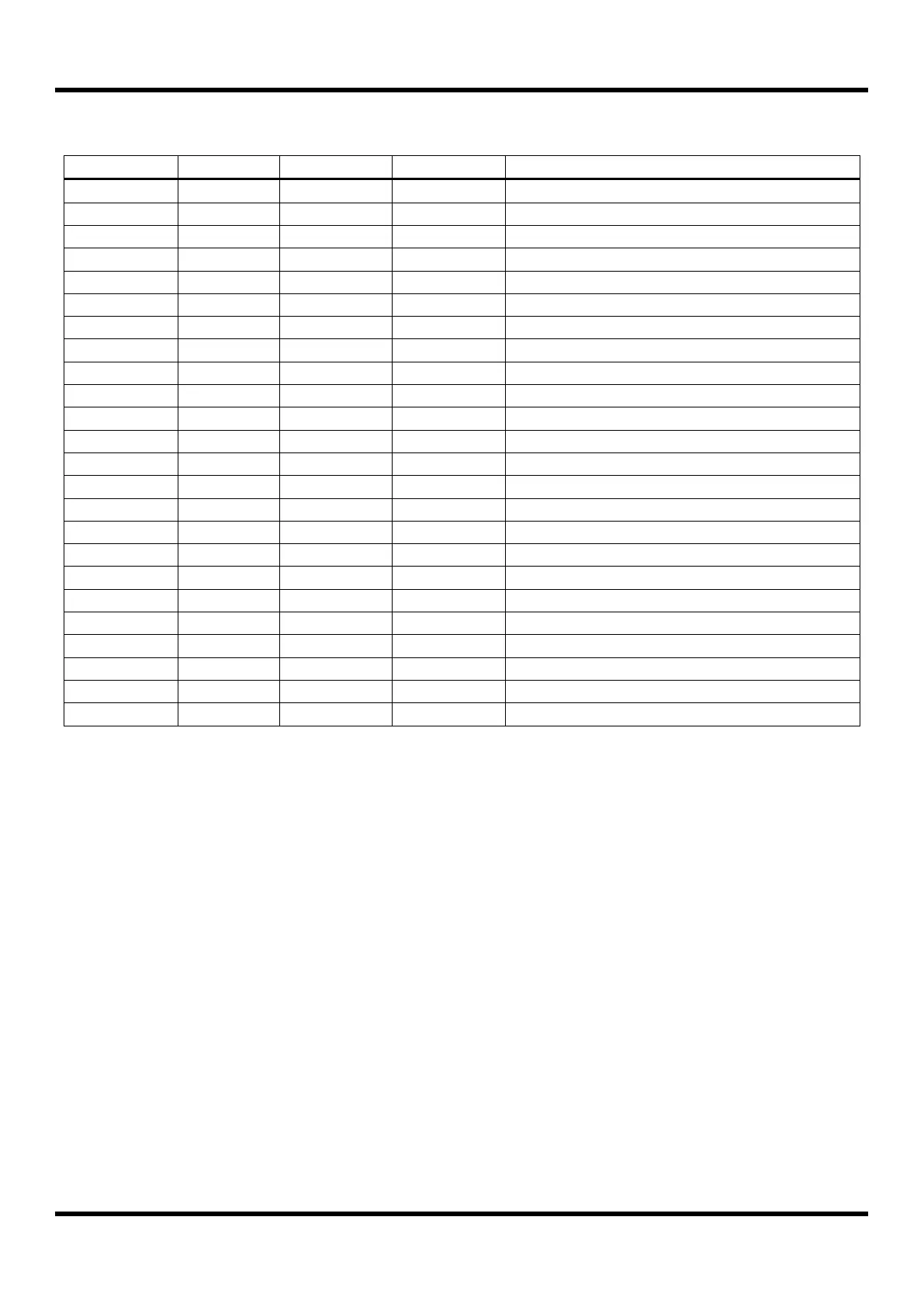

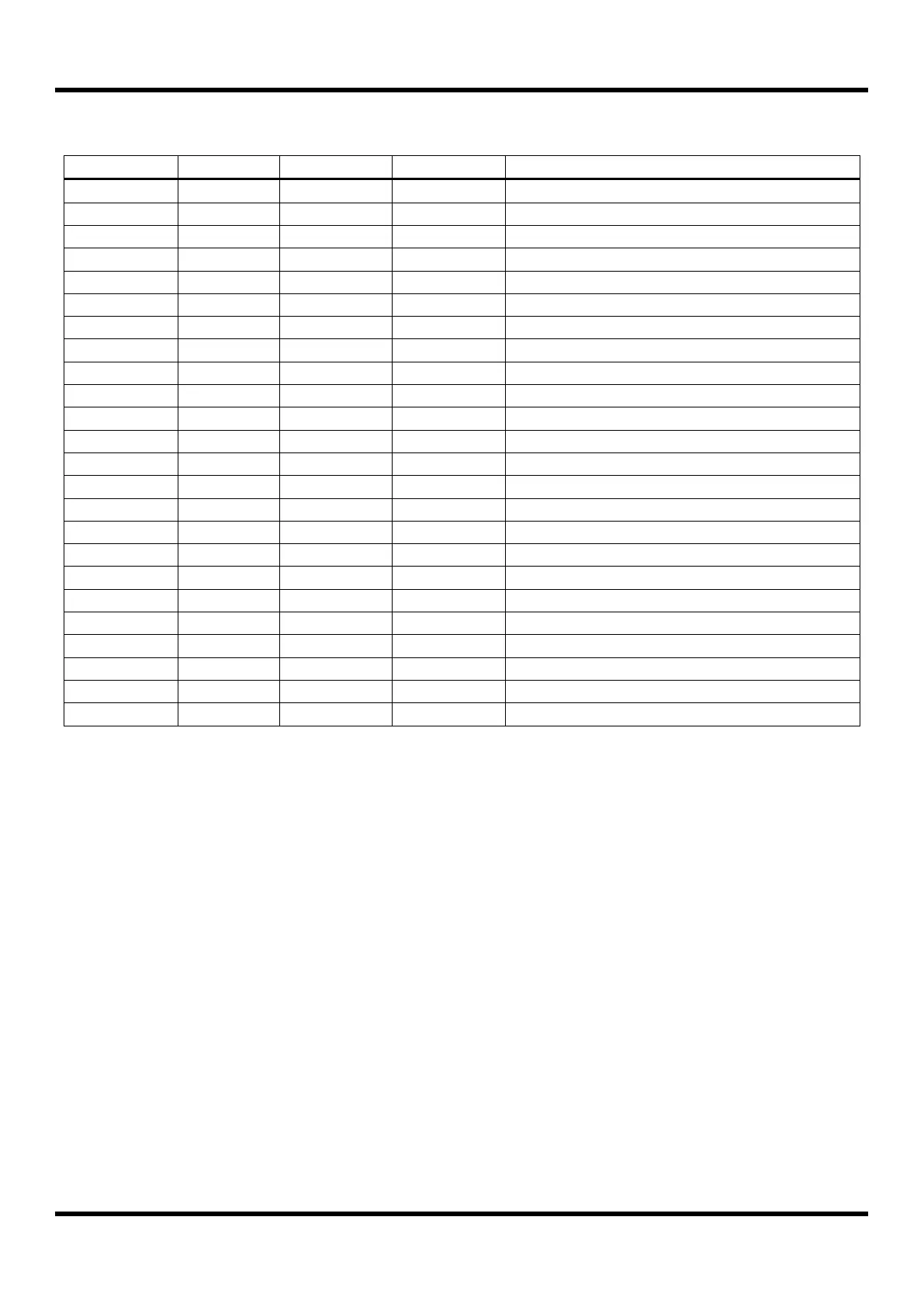

11.12.22 Register Map

USI0 Baud Rate Generation Register

USI0 SDA Hold Time Register

USI0 SCL High Period Register

USI0 SCL Low Period Register

USI0 Slave Address Register

USI1 Baud Rate Generation Register

USI1 SDA Hold Time Register

USI1 SCL High Period Register

USI1 SCL Low Period Register

USI1 Slave Address Register

Table 11.21 USI Register Map

11.12.23 USIn Register Description

USIn module consists of USIn baud rate generation register (USInBD), USIn data register (USInDR), USIn SDA hold

time register (USInSDHR), USIn SCL high period register (USInSCHR), USIn SCL low period Register (USInSCLR),

USIn slave address register (USInSAR), USIn control register 1/2/3/4 (USInCR1/2/3/4), USIn status register 1/2

(USInST1/2).

Loading...

Loading...