170

ABOV Semiconductor Co., Ltd.

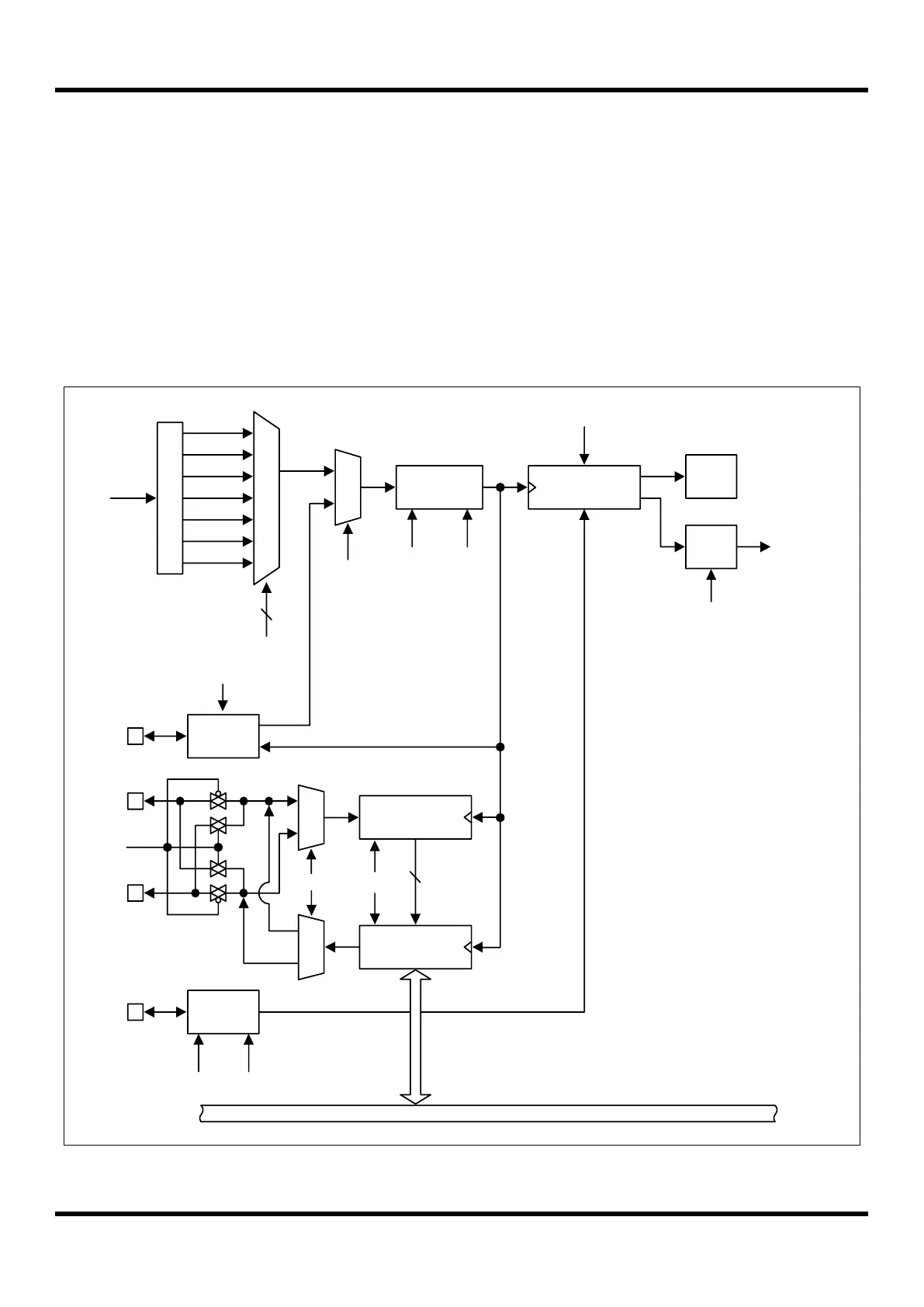

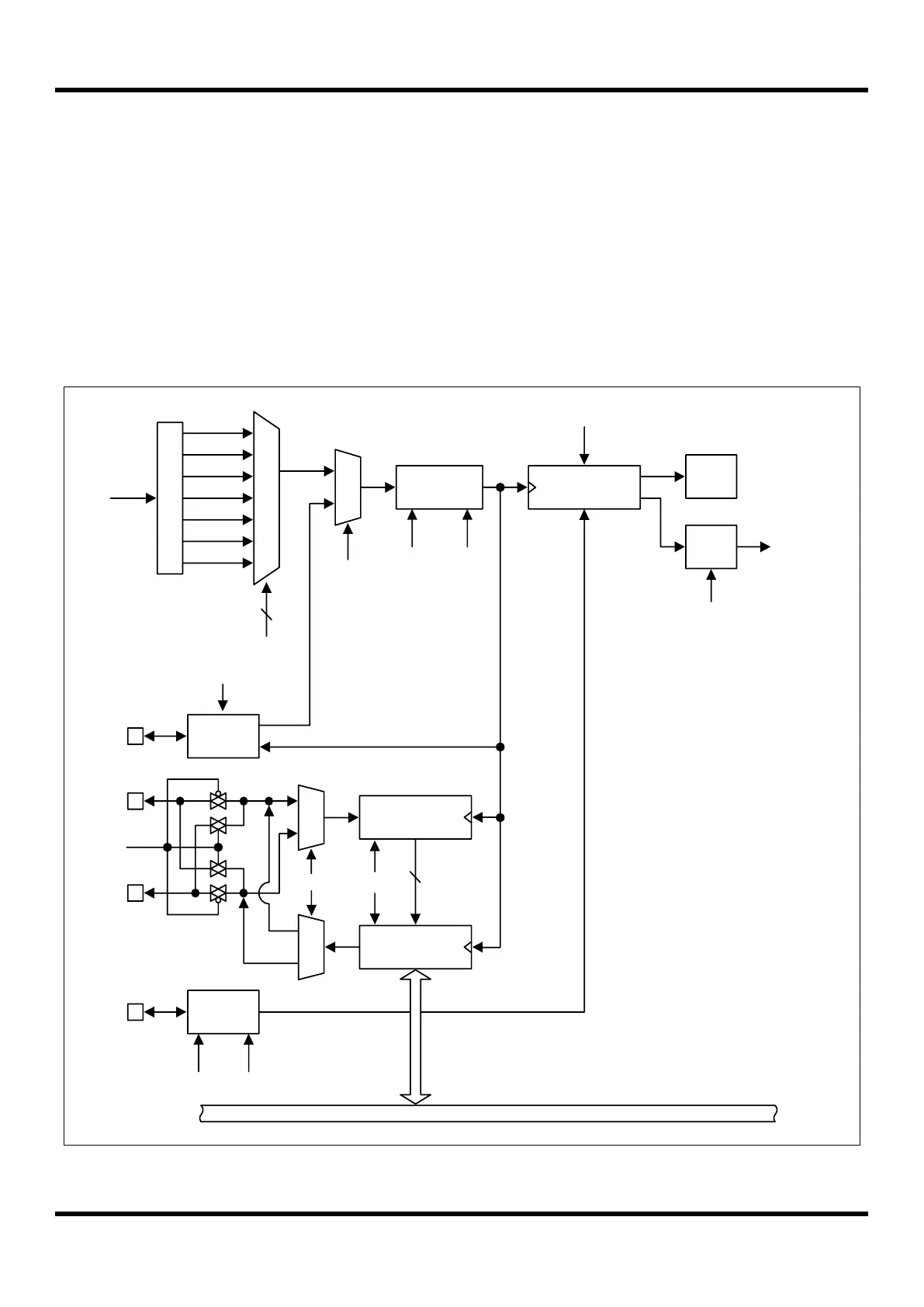

11.10 SPI 2

11.10.1 Overview

There is serial peripheral interface (SPI 2) one channel in MC96F6432S. The SPI 2 allows synchronous serial data

transfer between the external serial devices. It can do Full-duplex communication by 4-wire (MOSI2, MISO2, SCK2,

SS2), support master/slave mode, can select serial clock (SCK2) polarity, phase and whether LSB first data transfer or

MSB first data transfer.

11.10.2 Block Diagram

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/4

fx/8

fx/32

fx/64

fx/128

fx/16

fx/2

SCK

Control

MS

SCK2

3

SPICR[2:0]

M

U

X

MS

CPHA

Edge

Detector

CPOL

SPI

Control Circuit

WCOL

SPIEN

INT_ACK

Clear

To interrupt

block

SPIIFR

8-bit Shift

Register

M

U

X

MS

SPIDR

(8-bit)

FLSB

8

D

E

P

MISO2

MOSI2

SS2

SS

Control

MSSSENA

Internal Bus Line

FXCH

Figure 11.49 SPI 2 Block Diagram

Loading...

Loading...