107

ABOV Semiconductor Co., Ltd.

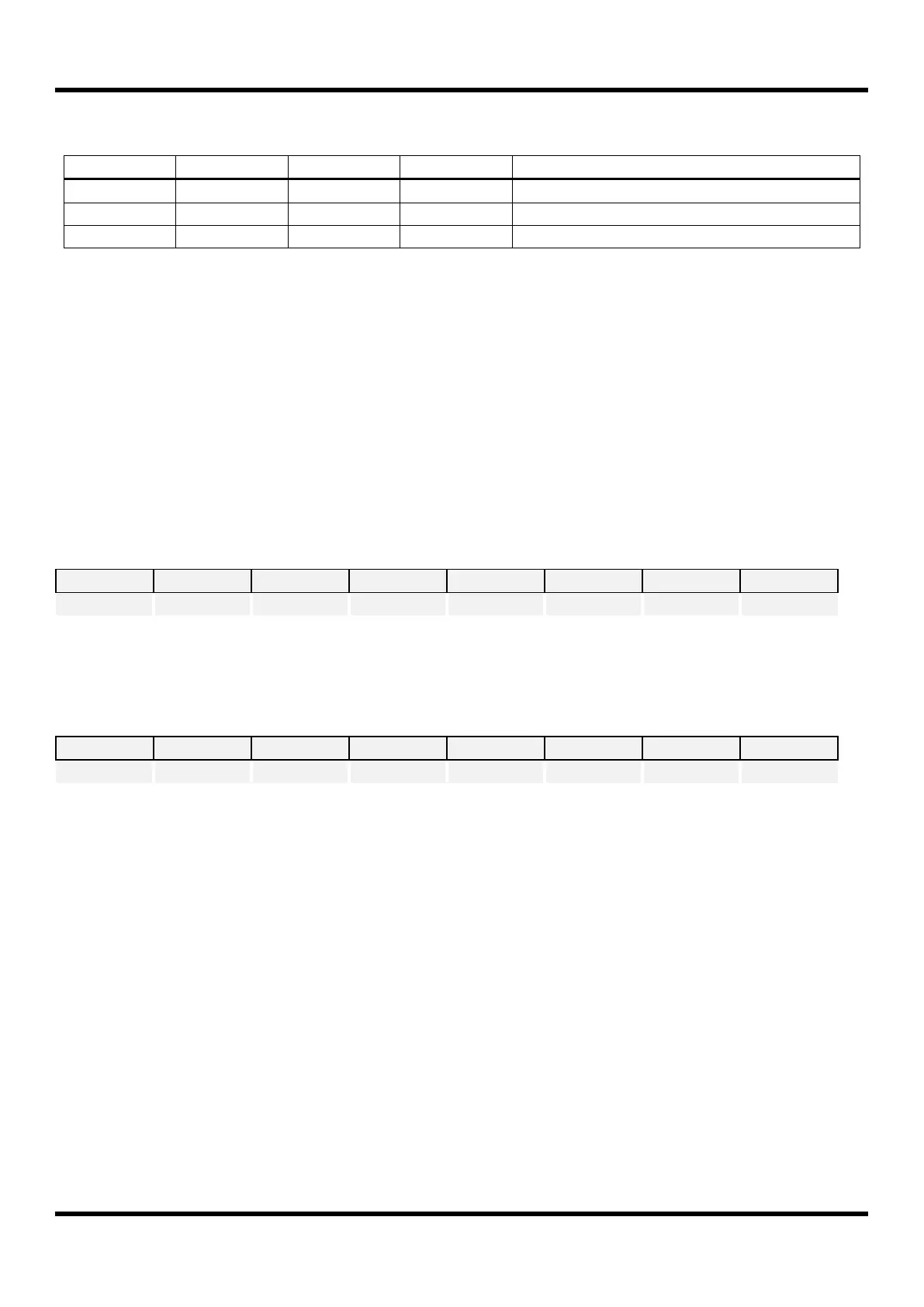

11.4.3 Register Map

Watch Timer Counter Register

Watch Timer Data Register

Watch Timer Control Register

Table 11.4 Watch Timer Register Map

11.4.4 Watch Timer Register Description

The watch timer register consists of watch timer counter register (WTCNT), watch timer data register (WTDR), and

watch timer controlregister (WTCR). AsWTCR is 6-bit writable/ readable register, WTCR can control the clock source

(WTCK[1:0]), interrupt interval (WTIN[1:0]), and function enable/disable (WTEN). Also there is WT interrupt flag bit

(WTIFR).

11.4.5 Register Description for Watch Timer

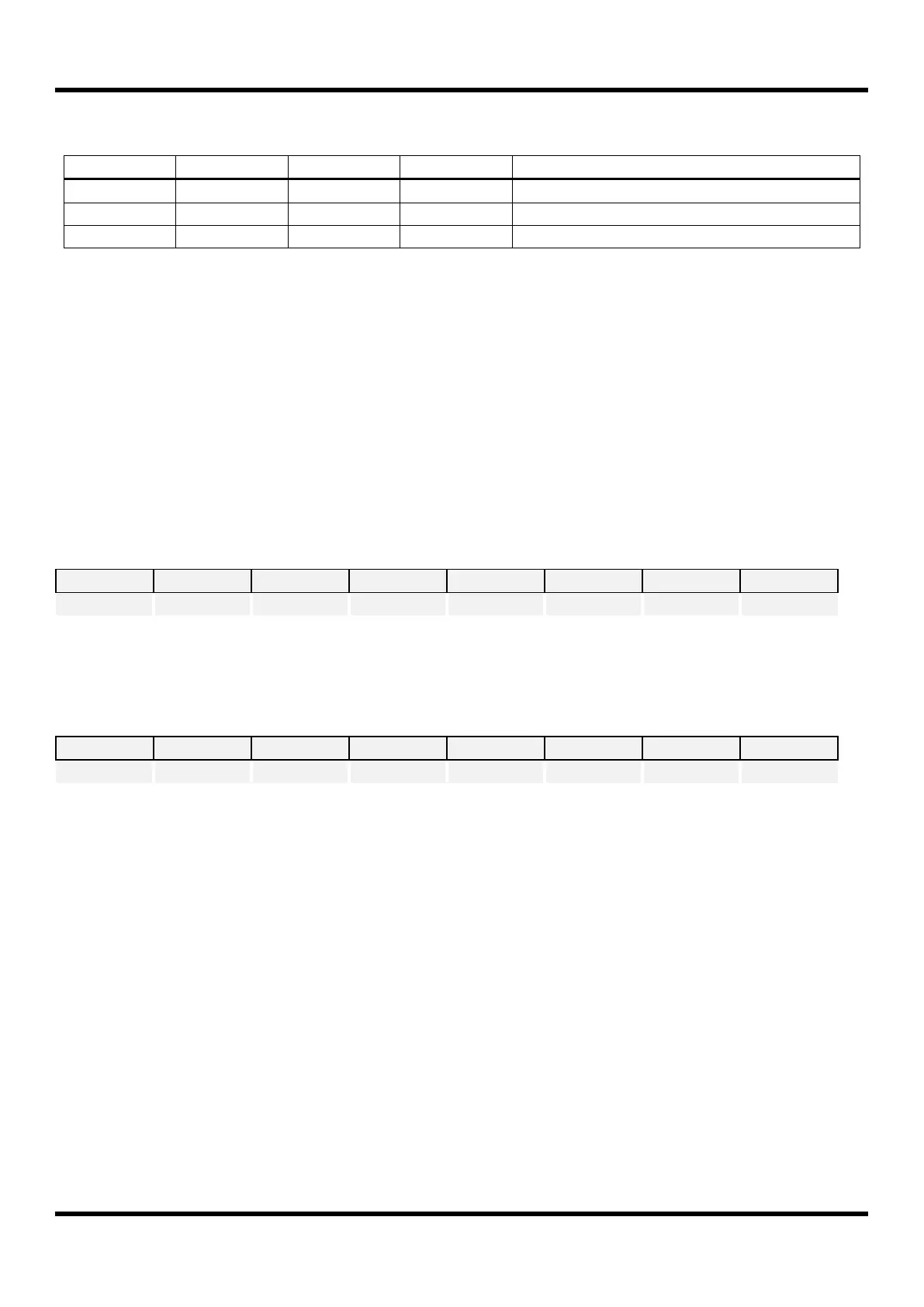

WTCNT (Watch Timer Counter Register: Read Case): 89H

Initial value: 00H

WTDR (Watch Timer Data Register: Write Case): 89H

Initial value: 7FH

Clear WT Counter (auto clear after 1 Cycle)

Set WT period

WT Interrupt Interval=fwck/(2^14 x(7bit WTDR Value+1))

NOTE)

1. Do not write “0” in the WTDR register.

Loading...

Loading...