179

ABOV Semiconductor Co., Ltd.

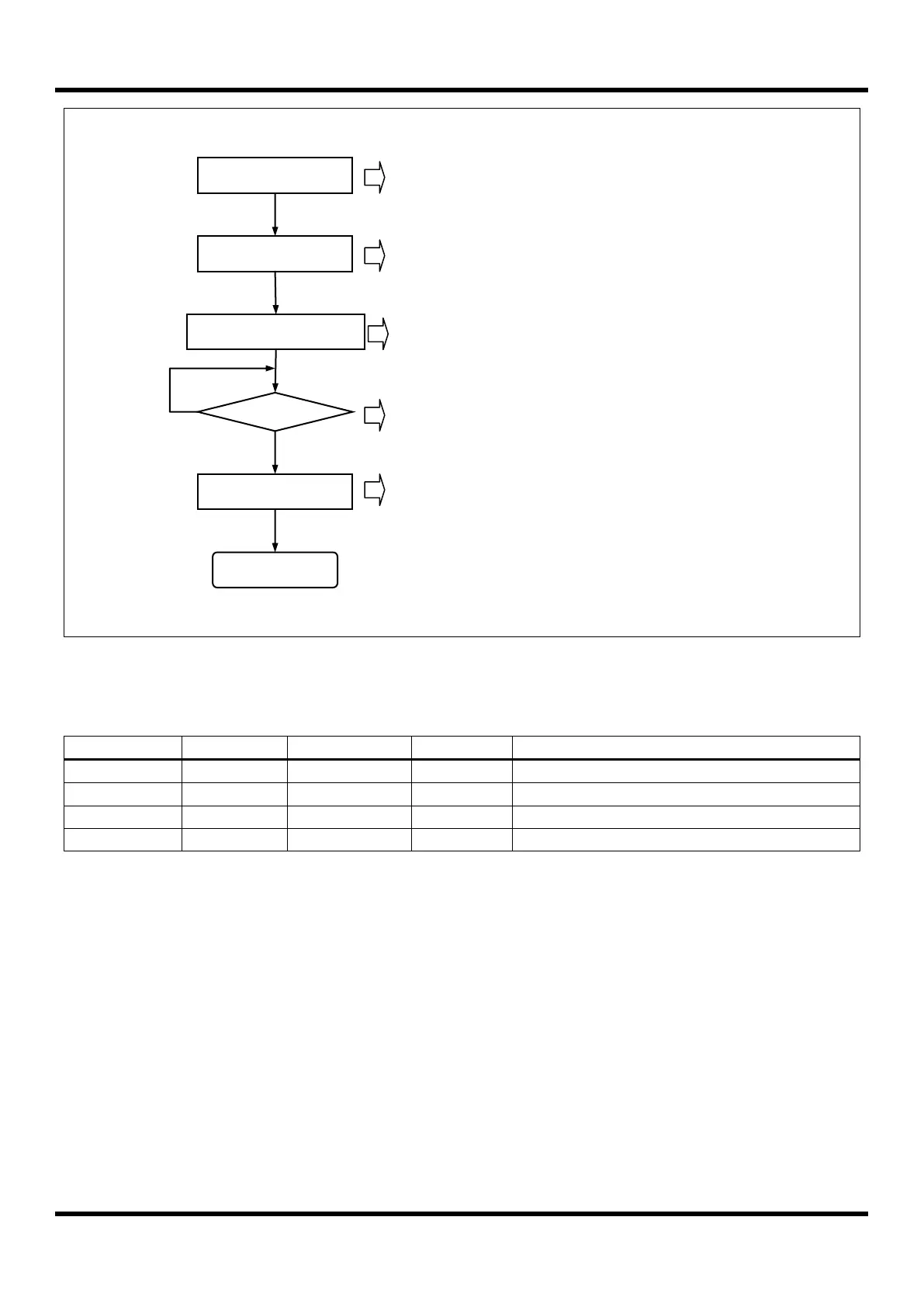

Figure 11.56 A/D Converter Operation Flow

11.11.5 Register Map

A/D Converter Data High Register

A/D Converter Data Low Register

A/D Converter Control High Register

A/D Converter Control Low Register

Table 11.18 ADC Register Map

11.11.6 ADC Register Description

The ADC register consists of A/D converter data highregister (ADCDRH), A/D converter datalowregister (ADCDRL),

A/D converter control high register (ADCCRH) and A/D converter control low register (ADCCRL).

Select ADC Clock and Data Align Bit.

ADC enable & Select AN Input Channel.

If Conversion is completed, AFLAG is set “1” and ADC

interrupt is occurred.

After Conversion is completed, read ADCDRH and ADCDRL.

Loading...

Loading...