115

ABOV Semiconductor Co., Ltd.

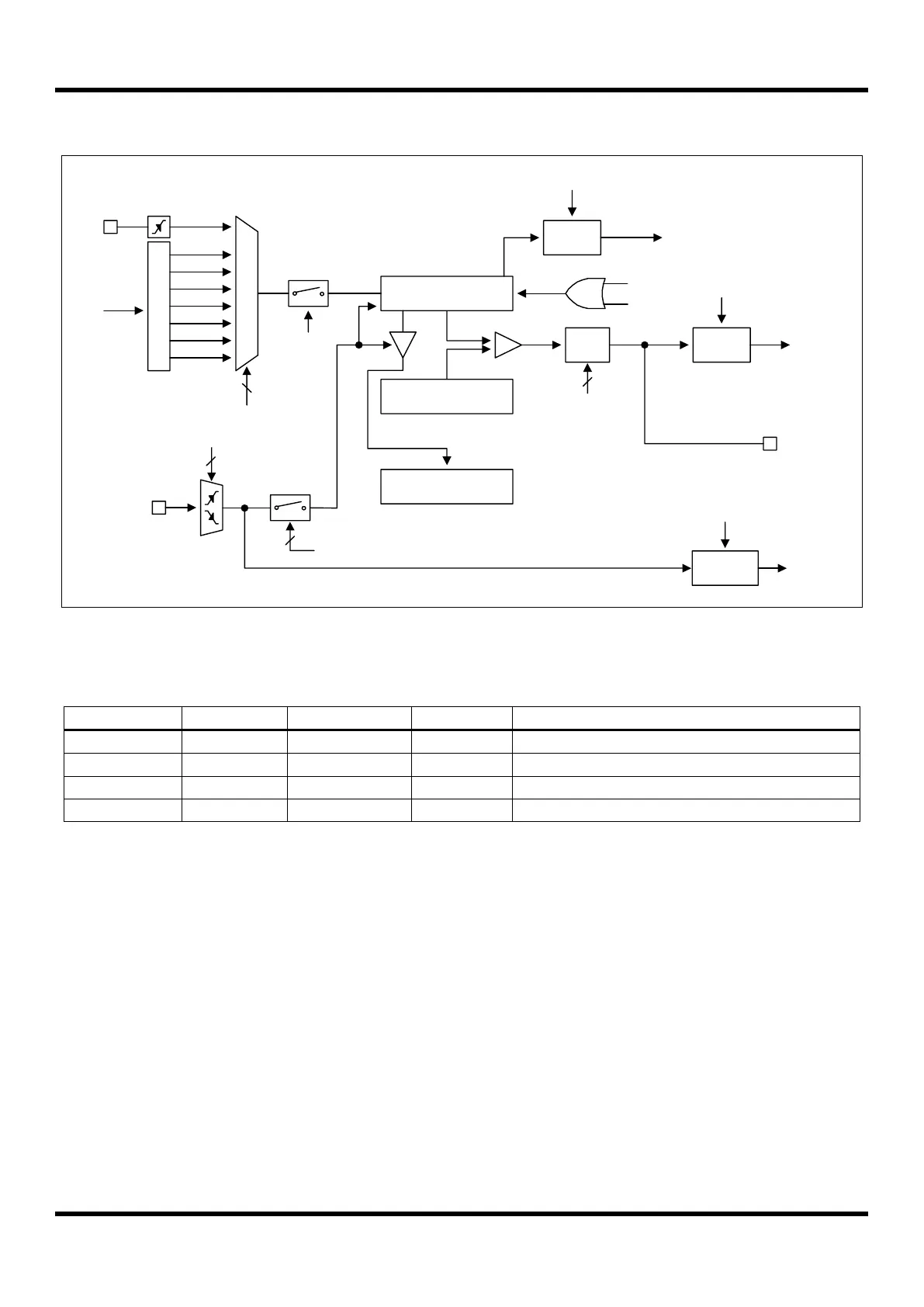

11.5.5 Block Diagram

INT_ACK

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

T0CNT (8Bit)

EC0

fx/4

fx/8

fx/32

fx/128

fx/512

fx/2048

3

T0CK[2:0]

T0EN

8-bit Timer 0 Counter

T0DR (8Bit)

Comparator

T0IFR

To interrupt

block

T0O/PWM0O

8-bit Timer 0 Data Register

INT_ACK

Clear

Clear

Match

MUX

T0CDR (8Bit)

Clear

T0OVIFR

To interrupt

block

Clear

EINT10

EIPOL1[1:0]

FLAG10

(EIFLAG1.0)

INT_ACK

Clear

To interrupt

block

2

T0MS[1:0]

2

T0MS[1:0]

2

Match signal

T0CC

Figure 11.13 8-bit Timer 0 Block Diagram

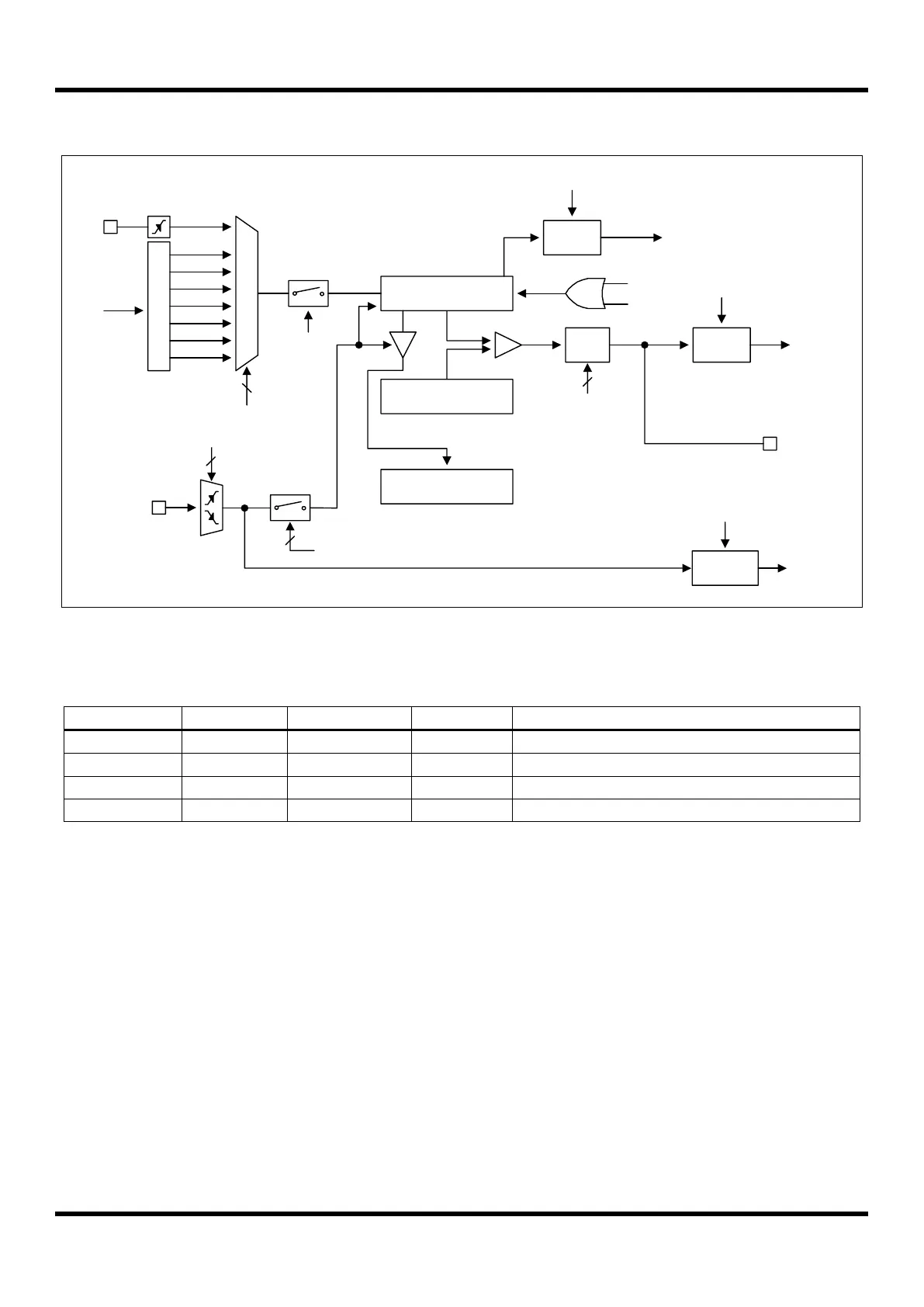

11.5.6 Register Map

Timer 0 Capture Data Register

Table 11.6 Timer 0 Register Map

11.5.7 Timer/Counter 0 Register Description

The timer/counter 0 register consists of timer 0 counterregister (T0CNT), timer 0 data register (T0DR), timer 0 capture

dataregister (T0CDR), andtimer 0 controlregister (T0CR). T0IFR and T0OVIFR bits are in the external interrupt flag 1

register (EIFLAG1).

Loading...

Loading...