200

ABOV Semiconductor Co., Ltd.

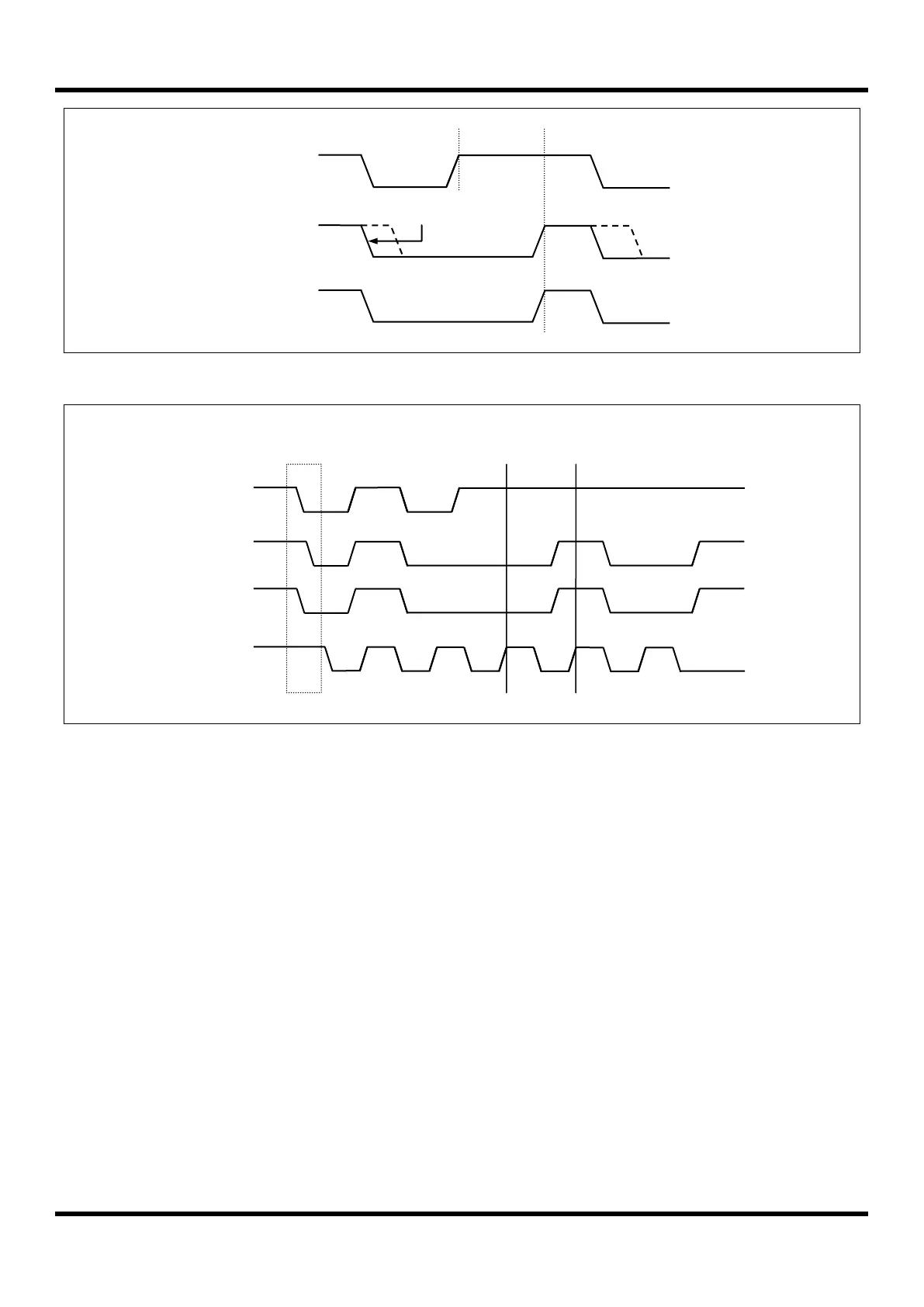

Figure 11.71 Clock Synchronization during Arbitration Procedure (USIn)

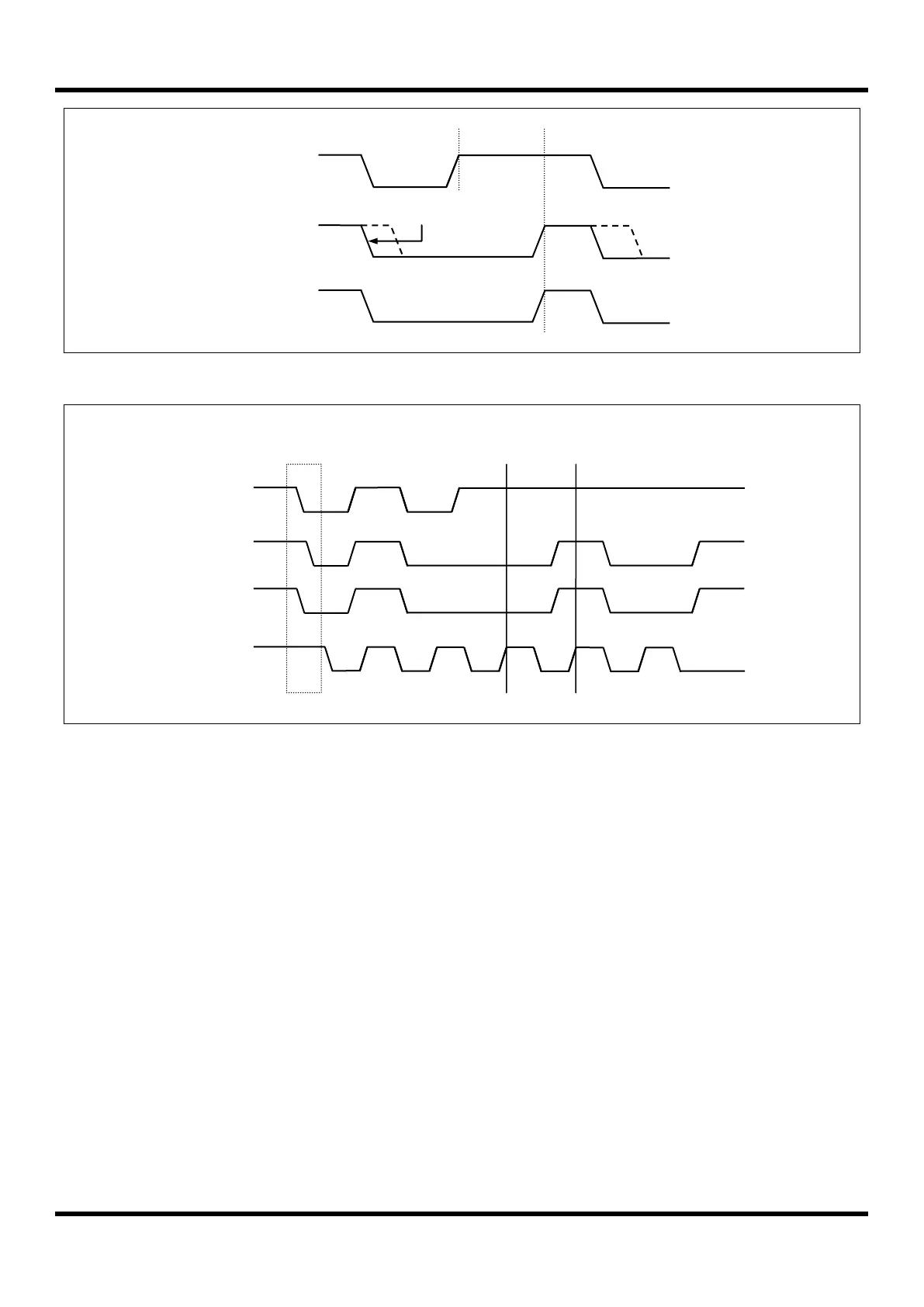

Figure 11.72 Arbitration Procedure of Two Masters (USIn)

11.12.20 USIn I2C Operation

The I2C is byte-oriented and interrupt based. Interrupts are issued after all bus events except for a transmission of a

START condition. Because the I2C is interrupt based, the application software is free to carry on other operations

during a I2C byte transfer.

Note that when a I2C interrupt is generated, IICnIFR flag in USInCR4 register is set, it is cleared when all interrupt

source bits in the USInST2 register are cleared to “0b”. When I2C interrupt occurs, the SCLn line is hold LOW until

clearing “0b” all interrupt source bits in USInST2 register. When the IICnIFR flag is set, the USInST2 contains a value

indicating the current state of the I2C bus. According to the value in USInST2, software can decide what to do next.

I2C can operate in 4 modes by configuring master/slave, transmitter/receiver. The operating mode is configured by a

winning master. A more detailed explanation follows below.

Arbitration Process

not adapted

Device 1 loses

Arbitration

Loading...

Loading...