90

ABOV Semiconductor Co., Ltd.

10.12.3 External Interrupt Flag Register (EIFLAG0, EIFLAG1)

The external interrupt flag 0 register (EIFLAG0) and external interrupt flag 1 register (EIFLAG1) areset to ‘1’ when the

external interrupt generating condition is satisfied. The flag is cleared when the interrupt service routine is executed.

Alternatively, the flag can be cleared by writing ‘0’ to it.

10.12.4 External Interrupt Polarity Register (EIPOL0L, EIPOL0H, EIPOL1)

The external interrupt polarity0 high/low register (EIPOL0H/L) and external interrupt polarity1 register

(EIPOL1)determines which type of rising/falling/both edge interrupt. Initially, default value is no interrupt at any edge.

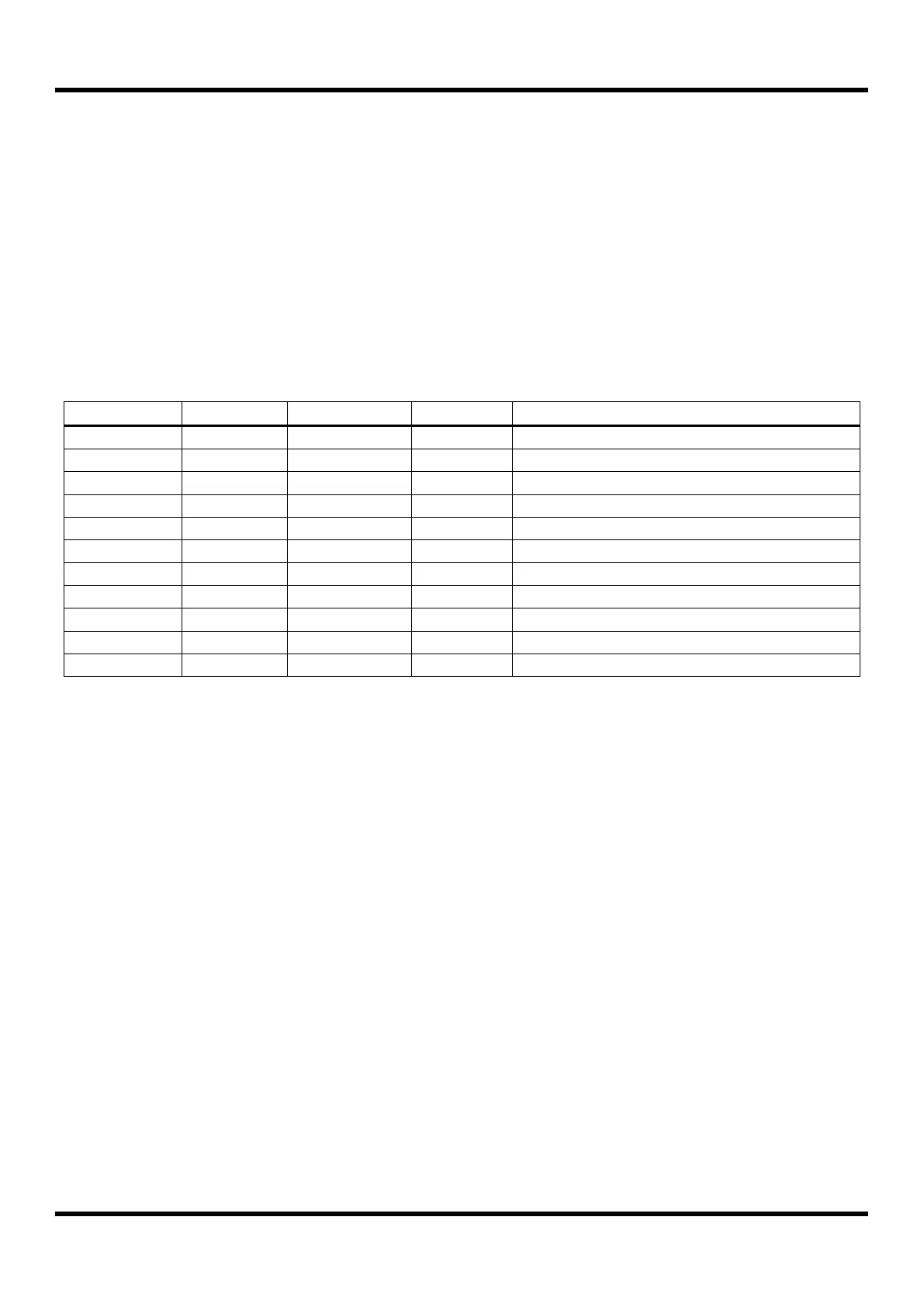

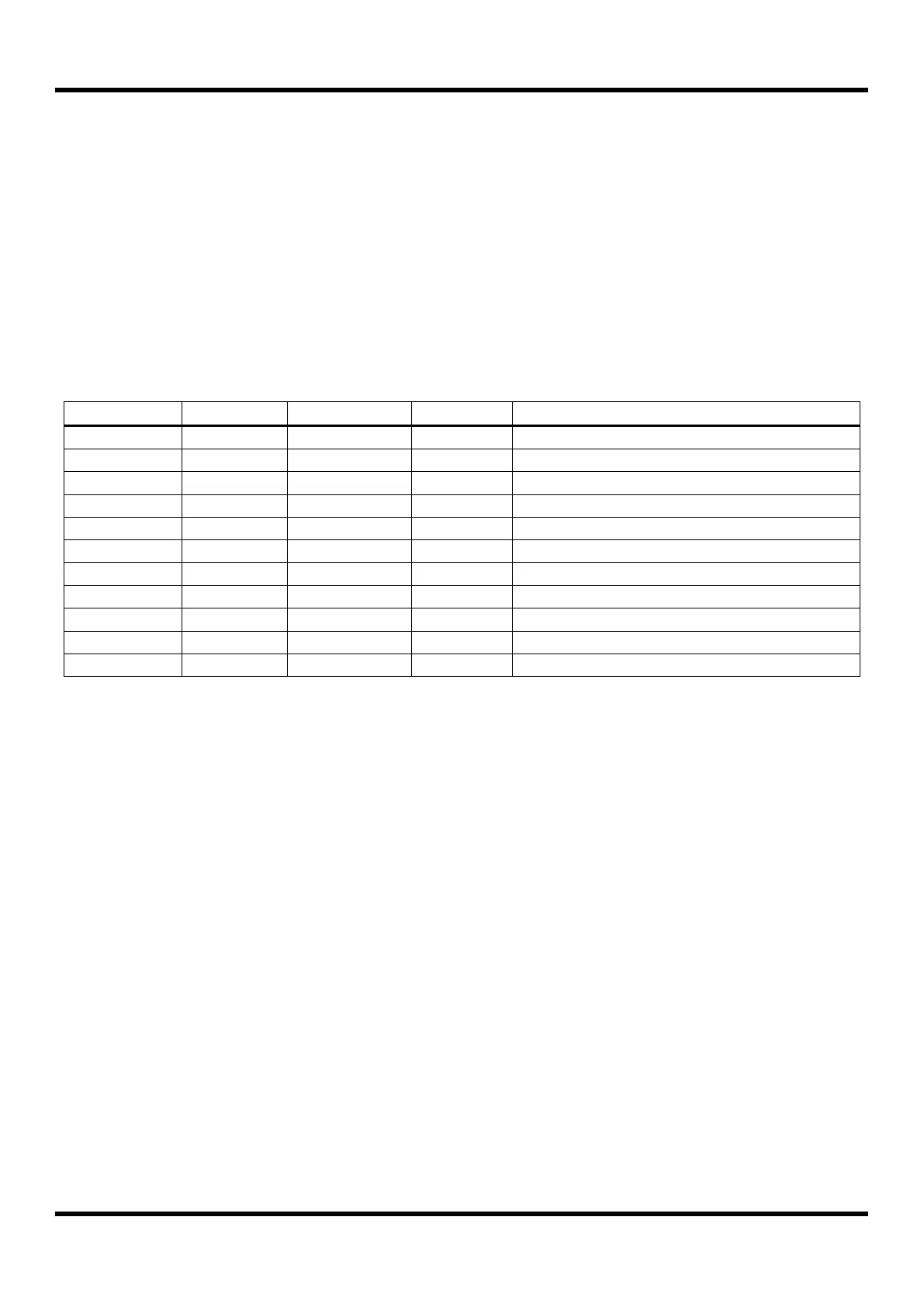

10.12.5 Register Map

Interrupt Enable Register

Interrupt Enable Register 1

Interrupt Enable Register 2

Interrupt Enable Register 3

Interrupt PriorityRegister

Interrupt PriorityRegister 1

External Interrupt Flag 0 Register

External Interrupt Polarity 0 Low Register

External Interrupt Polarity 0 High Register

External Interrupt Flag 1 Register

External Interrupt Polarity 1 Register

Table 10.3 Interrupt Register Map

10.12.6 Interrupt Register Description

The interrupt register is used for controlling interrupt functions. Also it has external interrupt control registers. The

interrupt register consists of interrupt enable register (IE), interrupt enable register 1 (IE1), interrupt enable register 2

(IE2) and interrupt enable register 3 (IE3). For external interrupt, it consists of external interrupt flag 0

register(EIFLAG0), external interrupt polarity 0 high/low register (EIPOL0H/L), external interrupt flag 1 register

(EIFLAG1) andexternal interrupt polarity 1 register(EIPOL1).

Loading...

Loading...