64

ABOV Semiconductor Co., Ltd.

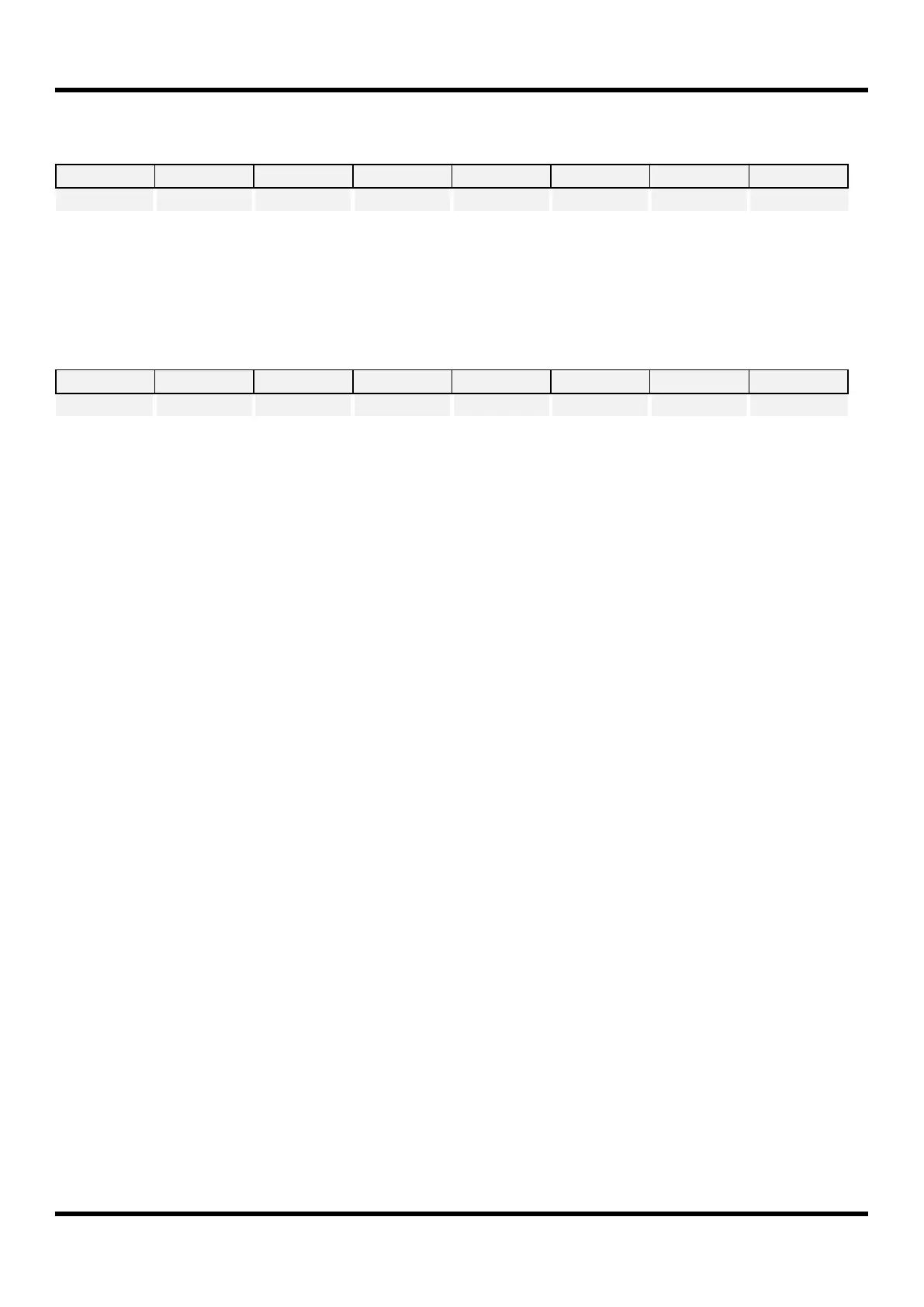

P0OD (P0 Open-drain Selection Register): 91H

Initial value: 00H

Configure Open-drain of P0 Port

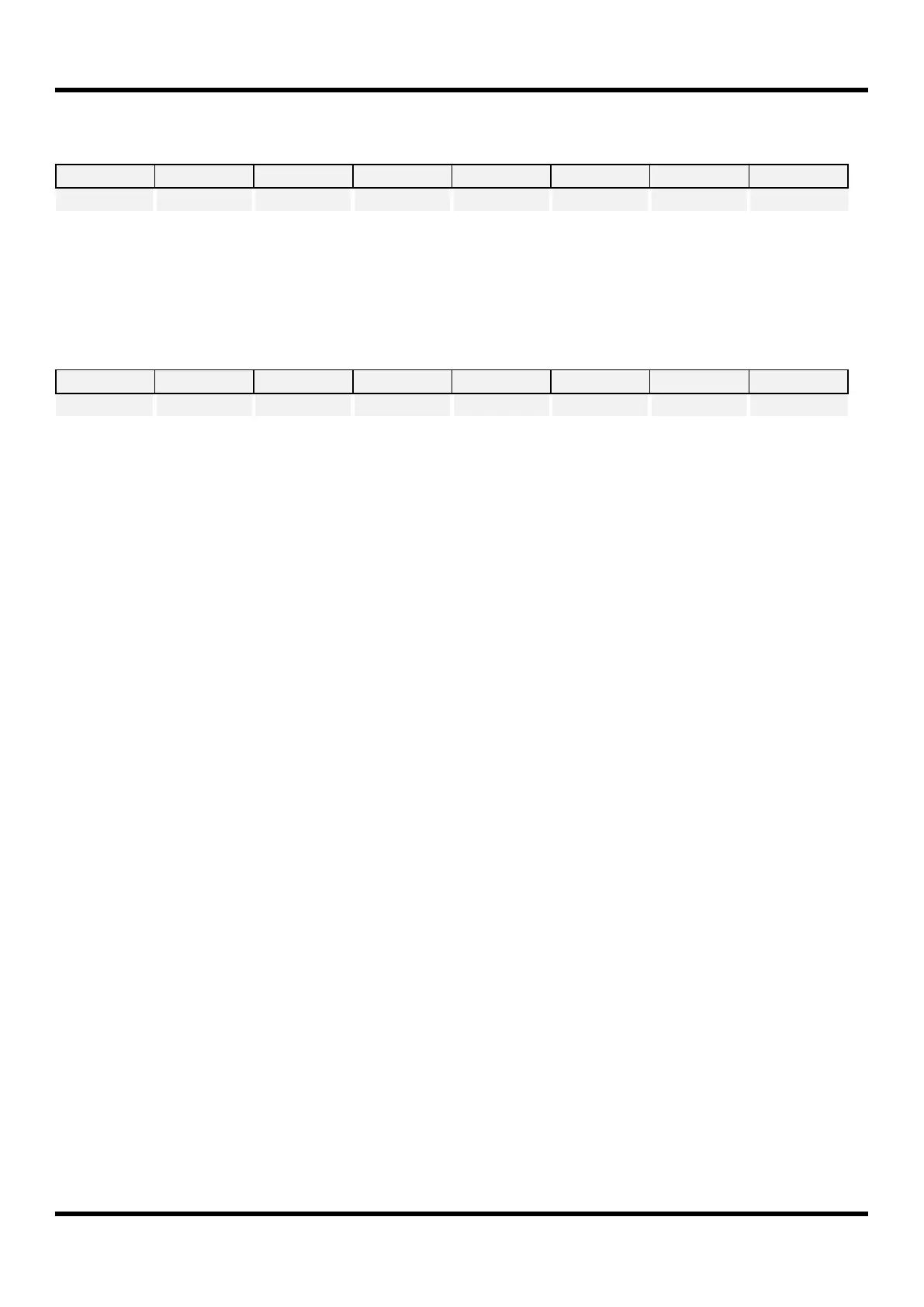

P0DB (P0 De-bounce Enable Register): DEH

Initial value: 00H

Configure De-bounce Clock of Port

Configure De-bounce of P07 Port

Configure De-bounce of P06 Port

Configure De-bounce of P05 Port

Configure De-bounce of P04 Port

Configure De-bounce of P03Port

Configure De-bounce of P02 Port

NOTE)

1. If the same level is not detected on enabled pin three or four times in a row at the sampling clock, the

signal is eliminated as noise.

2. A pulse level should be input for the duration of 3 clock or more to be actually detected as a valid edge.

3. The port de-bounce is automatically disabled at stop mode and recovered after stop mode release.

Loading...

Loading...