SOURCE

A26 HIGH STABILITY

FREQUENCY REFERENCE

(OPTION 1D5)

10 MHz

10 MHz ADJ

A59 SOURCE INTERFACE

CONTROL

AND

BIAS

EXT

AM

LOW BAND ADJ

ALC

OFFSET

SLOPE

LO MED HI

BLANKING ADJ

SOURCE CONTROL SWITCHES FROM A9

LOWBAND

OSCILLATORS

M/A/D/S

A11 PHASE LOCK

10 MHz

PRECISION

REFERENCE

EXT

REF IN

JUMPER (ONLY USED WITH OPTION 1D5)

PLL FROM

SOURCE

CONTROL

BOARD

10

1st IF 10 MHz

PL REF

1 MHz

PRETUNE

DAC

PRETUNE

FM YIG1

RED LED

"UNLOCK"

RED LED

NORMAL= FLASHING

AMBER LED

"PULL DOWN"

MAIN YIG1

A55 YIG1

A68

ATTN

2.55-20 GHz

W7

A29

A20

W6

W3

W11

3.8 GHz

A53

MIXER/

AMP

A57

FIXED

OSC

A58 M/A/D

J1

J2

STEP

RECOVERY

DIODE

A52 PULSE

GENERATOR

A14 FRACTIONAL-N (DIGITAL)

4

4

N

VCO

60 TO 240 MHz

COUNTER

INPUTS

v

COUNT

GATE

(23)

A13 FRACTIONAL-N (ANALOG)

API ADJ

100 kHZ

FROM A12

API s

TO A10

LSWP

VCXO

40 MHz

10 MHz

1 MHz

4 MHz TO A10

16 kHz

VCXO ADJ

W2

f(11) IF

F=40 MHz

v(12) IF DET

A12 REFERENCE

v(8)

SWPERR

+0.25/GHz

v (9)

f(17) PL REF

V(18)

v(15) VCO TUNE

VCXO

TUNE

39.984 MHz

f(16) 2nd LO 9.996 MHz

40 MHz

v(13)

EXT REF

VCO

W40

W42

0.05-2.55 GHz

LOWBAND

J3

POWER

A15 PREREGULATOR

A8 POST-REGULATOR

REGULATORS

SWITCHING

POWER

SUPPLY

AND

REGULATOR

A51 TEST SET

INTERFACE

CONTROL

AND

BIAS

STEP

ATTENUATORS

TRANSFER SWITCH

LOWER FT. PANEL

BIAS TO BIAS TEE'S

NORMAL= ON, STEADY

9 GREEN LEDS

NORMAL= OFF

NORMAL= ON

GREEN LED

RED LED

LINE

POWER

A15W1

FAN POWER

MICROCIRCUIT POWER

INSTRUMENT POWER

+25V

+18V

+8V

-8V

-18V

+5VD

A16 REAR PANEL

TEST SET-I/0

INTERFACE

TEST SET-I/0

INTERFACE

EXT BIAS

EXT REF

AUX INPUT

EXT TRIG

EXT AM

TEST SEQ

LIMIT TEST

MEAS RESTART

TO A17

TO A12

TO A10

TO A17

FROM A9

TO A17

A7 CPU

DIN KYBD

INTERCONNECT

RS-232

INTERCONNECT

PARALLEL

INTERCONNECT

GPIB

INTERCONNECT

A1 FRONT PANEL

MEASURE

RESTART

A21

KEYBOARD

RPG

FRONT

PANEL

PROCESSOR

A2 FRONT PANEL INTERFACE

A3 DISK

DRIVE

A22 DISPLAY

INTERFACE

VGA

INTERFACE

VGA

INTERCONNECT

+5 VD

FROM A17

TO A22

TO A9

TO A10

TO A51

TO A12

TO A11

TO A14

A19 GSP

DIGITAL

INTERFACE

VIDEO

PALETTE

MEMORY

A18 DISPLAY

TFT

LIQUID

CRYSTAL

DISPLAY

(LCD)

XXX

LIGHT

CAUTION

1.5KV AC START UP

680V AC STEADY STATE

A20

INVERTER ASSY

RECEIVER

A10 DIGITAL IF

TIMING

CONTROL

ADC

ANALOG

BUS

AUX IN

A17

A5 2nd CONNVERTER

1/2

4 MHz FROM A12

SAMPLE

RATE IS

16 kHz

A OUT

B OUT

R OUT

IFA 4 kHz

IFB 4 kHz

IFR 4 kHz

TP18

TP20

TP16

INSTRUMENT

NODES

LSWP (FROM A14)

EXT TRIG

A9 SOURCE CONTROL BOARD

SOURCE

CONTROL

SWITCHES TO

A59

W47

W48

W2

S11

S12

TRL

CAL

S11

S21

S12

S22

FWD

TRL

CAL

S21

S22

W49

W23

W34

W21

SAMPLER

BIAS

A65 A SAMPLER

A66 B SAMPLER

F=30 MHz

F=30 MHz

F=30 MHz

F=30 MHz

J2

J2

J2

J2

J1

J1

J1

A64 R1 SAMPLER

A67 R2 SAMPLER

J3

J3

J3

J3

MOTHERBOARD

v(1)

+0.37V

v(2)

+2.5V

v(4)

A10 GND

AUX

INPUT

v(3)

A4 2nd CONVERTER

A6 2nd CONVERTER

PLL OUT TO

PHASE LOCK BD.

S

S

S

S

J1

J2

100 kHz TO A13

f(14) 100kHz

SIGNAL SEPARATION: OPT 400, 012

A56 LOWER

FRONT

PANEL

A61 BIAS TEE

A60 BIAS TEE

A62 DIRECTIONAL

COUPLER

A63 DIRECTIONAL

COUPLER

W39

0-55dB

0-55dB

S12/S22

S11/S21

TO A51

PORT 1

PORT 2

W25

W26

PORT 1

PORT 2

W17

OUT

W30

NON-OPT 012

NON-OPT 012

A

IN

W52

W16

OPT 012

W14

W52

W22

W15

OUT

IN

OPT 012

B

A73 BUFFER

AMP

DIN KYBD PORT

INTERFACE

RS-232 PORT

INTERFACE

PARALLEL PORT

INTERFACE

GPIB PORT

INTERFACE

DIGITAL SIGNAL

PROCESSOR

ROM RAM

ADC

REG

EEPROM

MAIN CPU

FLASH

RAM

MAIN RAM

CONTROL/REFRESH

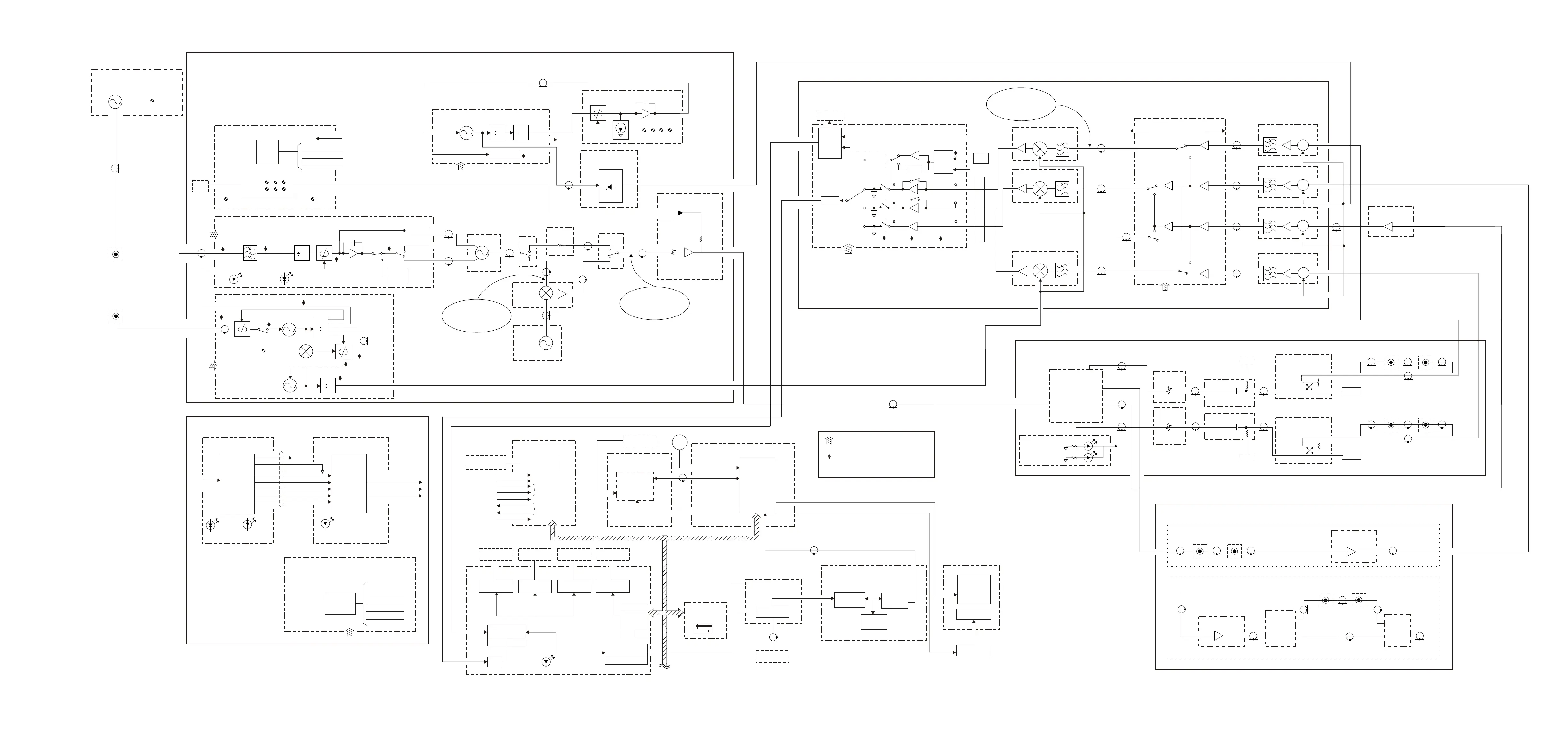

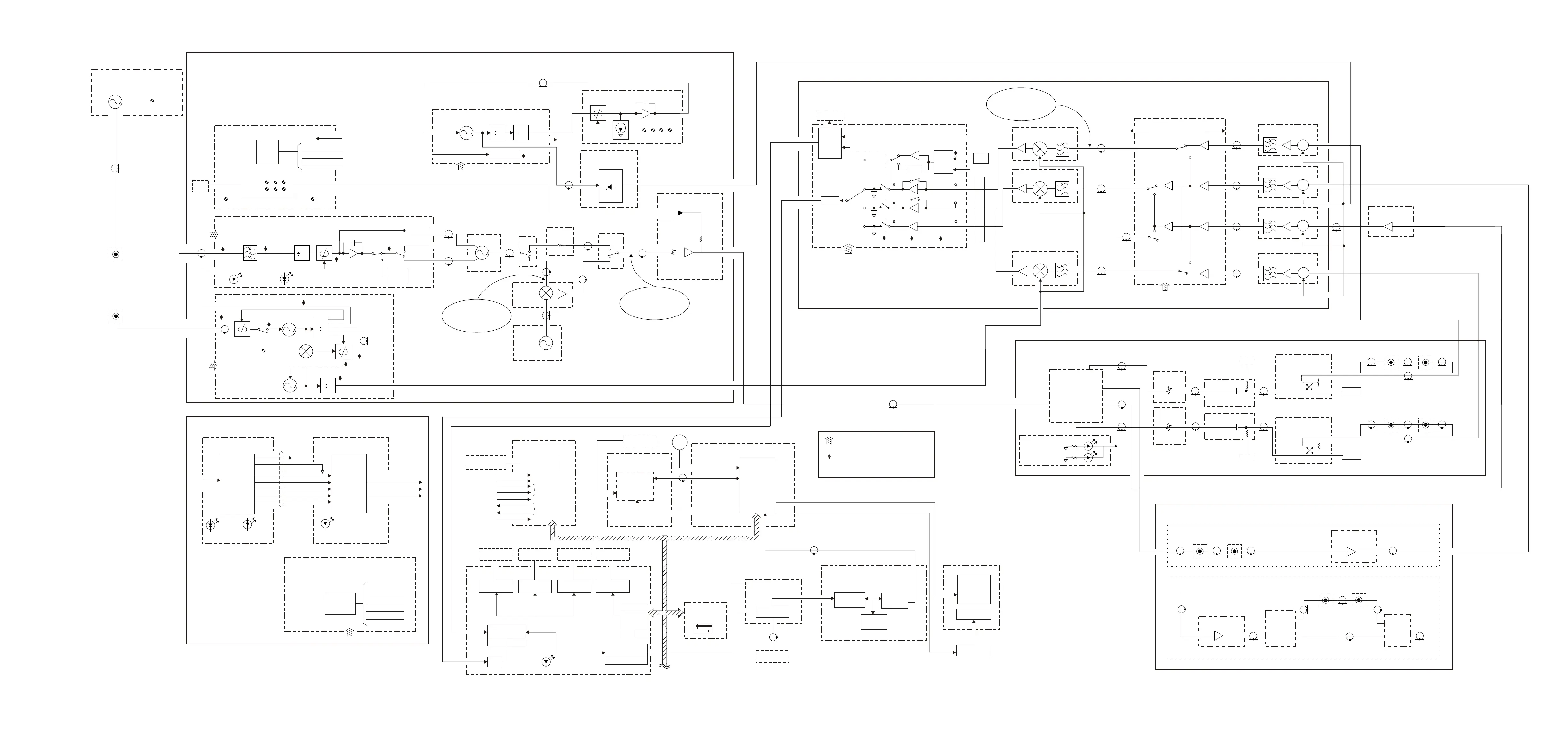

8719ES/8720ES OVERALL BLOCK DIAGRAM FOR OPT 400, 012, 089, 1D5

8719ES/8720ES OVERALL BLOCK DIAGRAM FOR OPT 400, 012, 089, 1D5

sb5107e

W32

A17

W35

W77

A70 STEP

ATTN

A71 STEP

ATTN

W41

W40

A74 SWITCH

SPLITTER

W55

OUT

OUT

W52

IN

IN

W33

A72 BUFFER

AMP

W36

A72 BUFFER

AMP

W50

A23

SWITCH

W54

W52

W18

W57

W53

A24

SWITCH

R1 LOOP: OPT 400, 089

NON-OPT 089

OPT 089

TO A74J3

TO A64J2

LEGEND

DIGITAL BUS

This indicates Analog Bus node location.

f = Frequency Node

v = Voltage Node

W88

W8

W82

W81

W1

W9

W31

W82

J2

J3

J4

J5

J1

J1

J1

J3

J3

J2

J2

J5

J6

J7

J8

J4

J3

J2

J1

W83

W99

W38

W37

W56

FM YIG2

MAIN YIG2

SRC TUNE

SET DAC # LOWBAND

» 4000 READ > 8 dBm

SRC TUNE

SET DAC # HIGH & MIDBAND

3200-4095 READ > 0 dBm

SET DAC # LOWBAND

3750-4095 READ > -5 dBm

CW 1 GHz

TEST PORT POWER -5 dBm

OPEN ON TEST PORT

10 MHz SINEWAVE 0.1V p-p

SMB TEE: A4, A5 OR A6

Loading...

Loading...