Rockwell Automation Publication 1756-RM003N-EN-P - October 2011 147

Timer and Counter Instructions (TON, TOF, RTO, TONR, TOFR, RTOR, CTU, CTD, CTUD, RES) Chapter 3

Execution:

Condition Relay Ladder Action

Prescan The .CD bit is set to prevent invalid decrements during the first program scan.

The rung-condition-out is set to false.

Rung-condition-in is false The .CD bit is cleared.

The rung-condition-out is set to false.

Postscan The rung-condition-out is set to false.

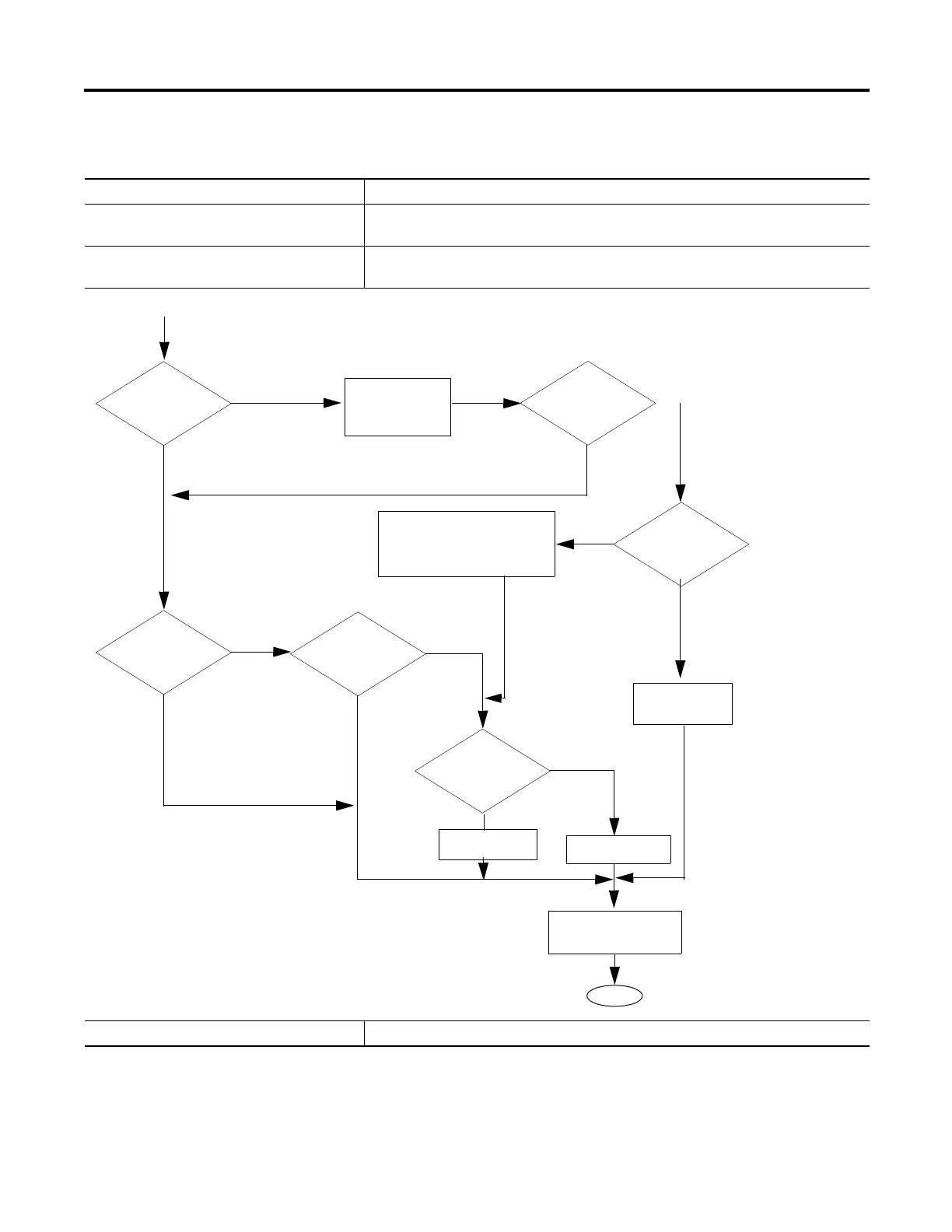

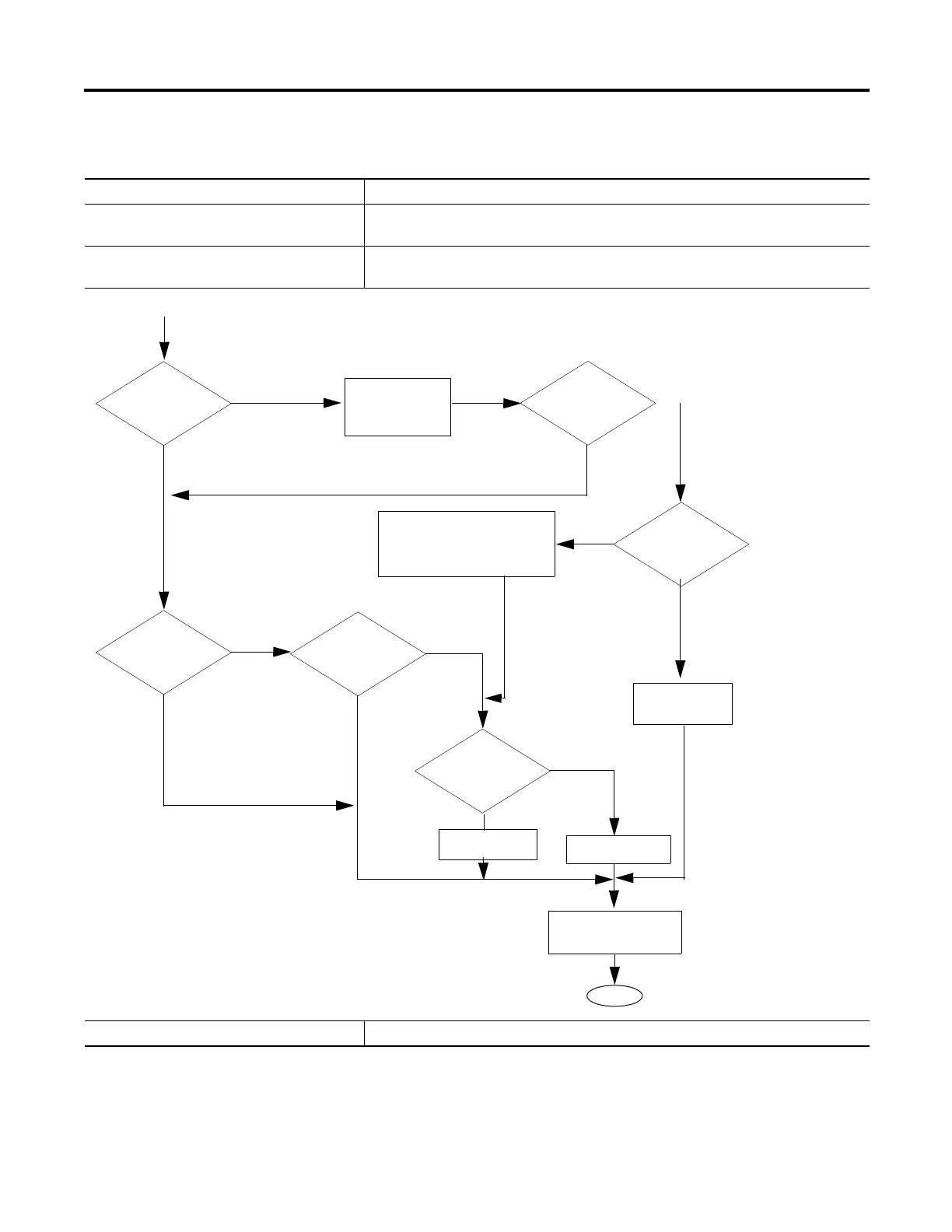

Examine .CD bit.

.CD Bit = 0

.CD bit = 1

Rung-condition-in is true

.ACC Value Rolls Over

Yes

No

Examine .UN Bit.

.UN bit = 0

.UN Bit = 1

.CD bit is set.

.ACC = .ACC - 1

Examine .OV Bit

.OV Bit = 0

Examine .OV Bit

.OV bit = 1

.OV bit is cleared.

.DN bit is cleared.

.UN bit is cleared.

.UN bit is set.

Examine .ACC

.ACC ≥ .PRE

.DN bit is set.

Rung-condition-out is set

to true.

End

.OV Bit = 1

.ACC < .PRE

.DN bit is cleared.

.OV bit = 0

Loading...

Loading...