AW00123409000 Physical Interface

Basler ace USB 3.0 81

For more information about GPIO pin assignments and pin numbering, see Section 5.2.1 on

page 68.

For more information about setting the GPIO line operation, see Section 5.11 on page 91 and

Section 5.12 on page 95.

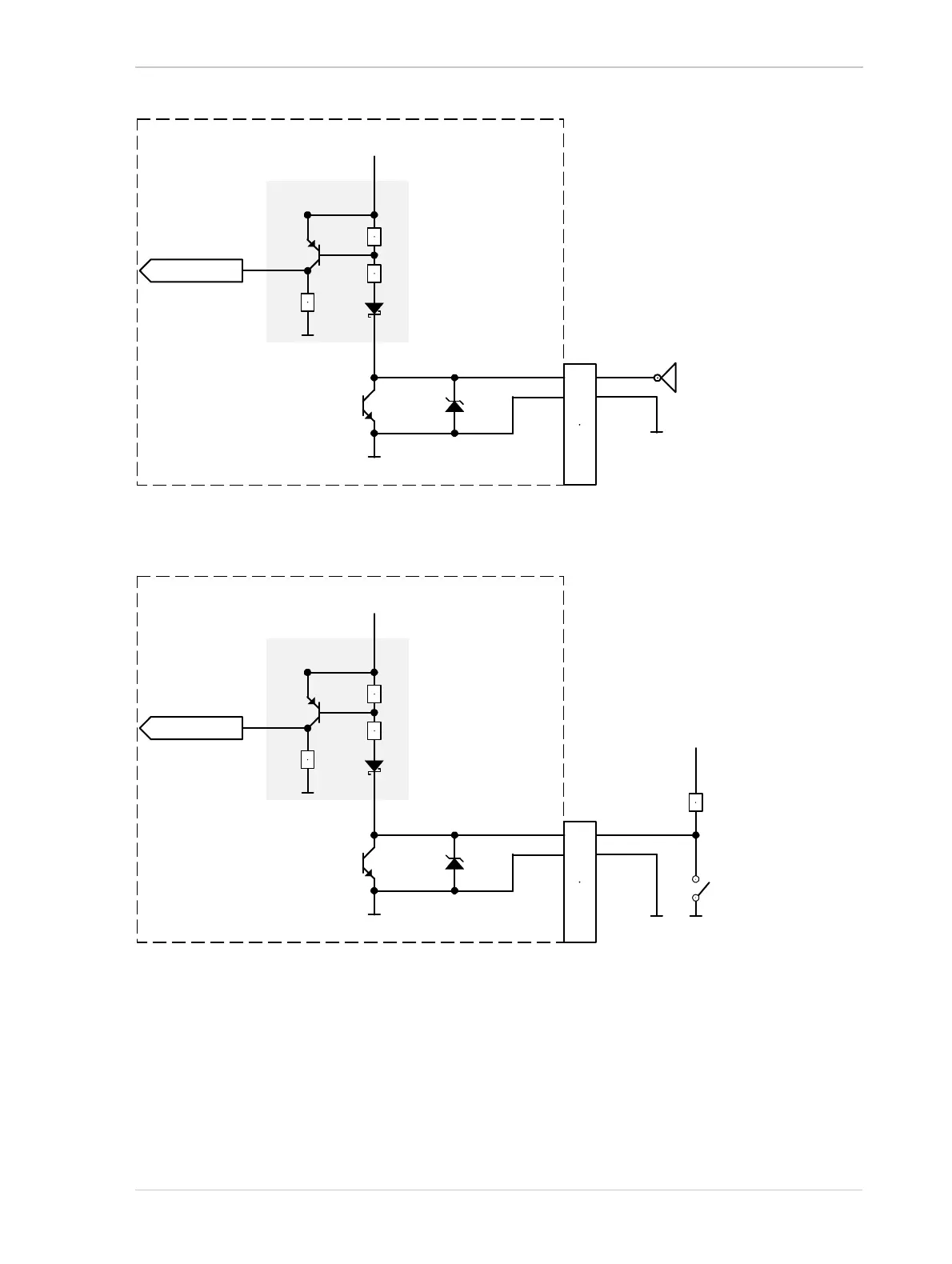

6-pin

Receptacle

6-pin

Receptacle

+3.3 VDC

(Typical)

1

6

3

4

2

5

Camera

Logic Gate

Input Buffer

FPGA Input

Ground for

Direct-coupled

GPIO

Fig. 43: Direct-coupled GPIO Line Schematic with the GPIO Line Set as an Input and with a Typical External Circuit

Using a Logic Gate (Illustration for Pin 1 as an Example; Simplified)

FPGA Input

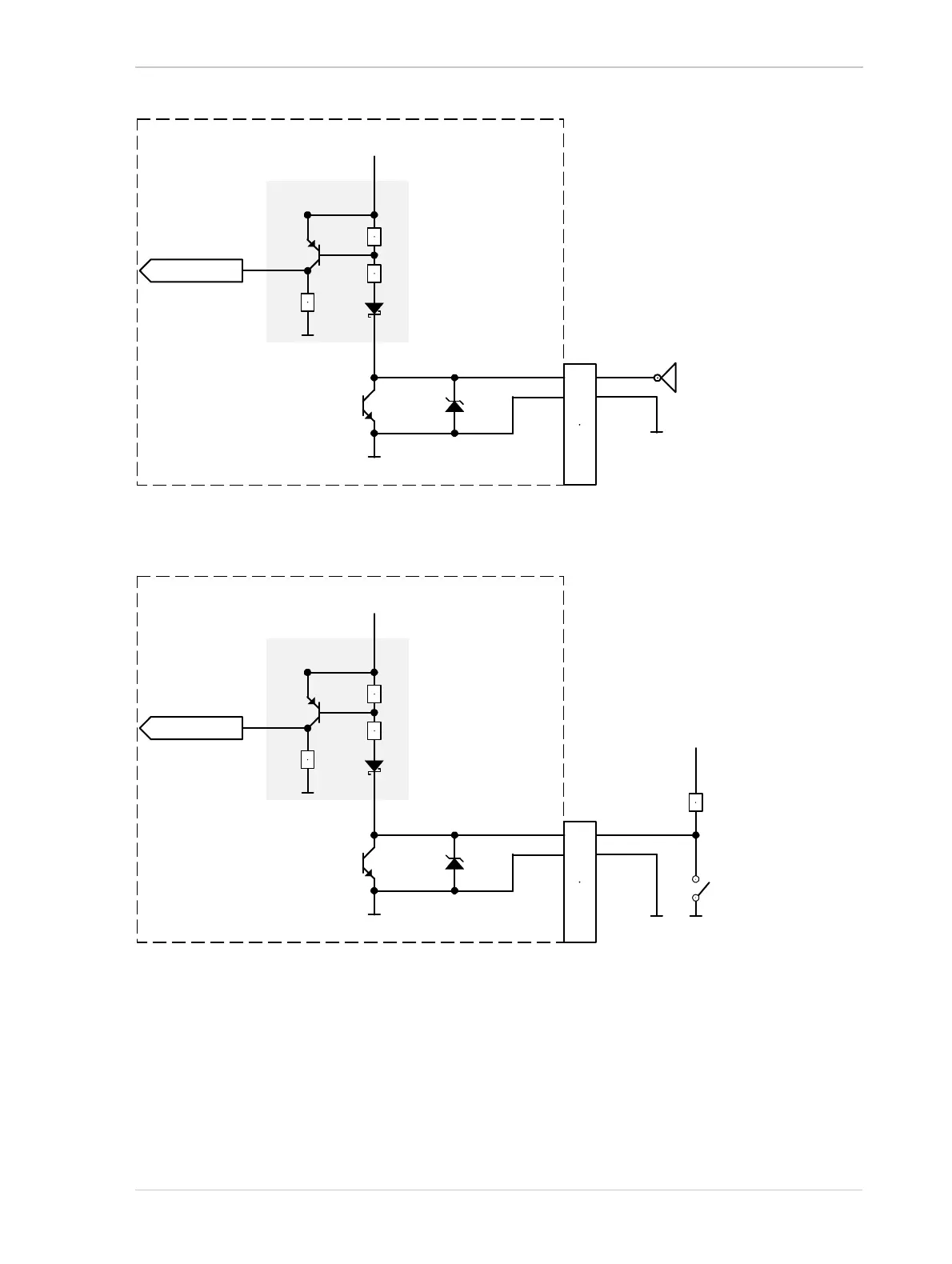

6-pin

Receptacle

+3.3 VDC

(Typical)

1

6

3

4

2

5

Camera

Input Buffer

+3.3 V ... +5.0 V

Ground for

Direct-

coupled

GPIO

Fig. 44: Direct-coupled GPIO Line Schematic with the GPIO Line Set as an Input and with a Typical External Circuit

(Illustration for Pin 1 as an Example; Simplified)

Loading...

Loading...