CENTRAL PROCESSING UNIT MC68332

5-18 USER’S MANUAL

5.10.2.2.1 External BKPT Signal

Once enabled, BDM is initiated whenever assertion of BKPT is acknowledged. If BDM

is disabled, a breakpoint exception (vector $0C) is acknowledged. The BKPT

input has

the same timing relationship to the data strobe trailing edge as does read cycle data.

There is no breakpoint acknowledge bus cycle when BDM is entered.

5.10.2.2.2 BGND Instruction

An illegal instruction, $4AFA, is reserved for use by development tools. The CPU32

defines $4AFA (BGND) to be a BDM entry point when BDM is enabled. If BDM is dis-

abled, an illegal instruction trap is acknowledged.

5.10.2.2.3 Double Bus Fault

The CPU32 normally treats a double bus fault, or two bus faults in succession, as a

catastrophic system error, and halts. When this condition occurs during initial system

debug (a fault in the reset logic), further debugging is impossible until the problem is

corrected. In BDM, the fault can be temporarily bypassed, so that the origin of the fault

can be isolated and eliminated.

5.10.2.2.4 Peripheral Breakpoints

CPU32 peripheral breakpoints are implemented in the same way as external break-

points — peripherals request breakpoints by asserting the BKPT

signal. Consult the

appropriate peripheral user's manual for additional details on the generation of periph-

eral breakpoints.

5.10.2.3 Entering BDM

When the processor detects a breakpoint or a double bus fault, or decodes a BGND

instruction, it suspends instruction execution and asserts the FREEZE output. This is

the first indication that the processor has entered BDM. Once FREEZE has been as-

serted, the CPU enables the serial communication hardware and awaits a command.

The CPU writes a unique value indicating the source of BDM transition into temporary

register A (ATEMP) as part of the process of entering BDM. A user can poll ATEMP

and determine the source (see Table 5-4) by issuing a read system register command

(RSREG). ATEMP is used in most debugger commands for temporary storage — it is

imperative that the RSREG command be the first command issued after transition into

BDM.

*Special status word (SSW) is described in detail in the

CPU32 Reference Manual

(CPU32RM/AD).

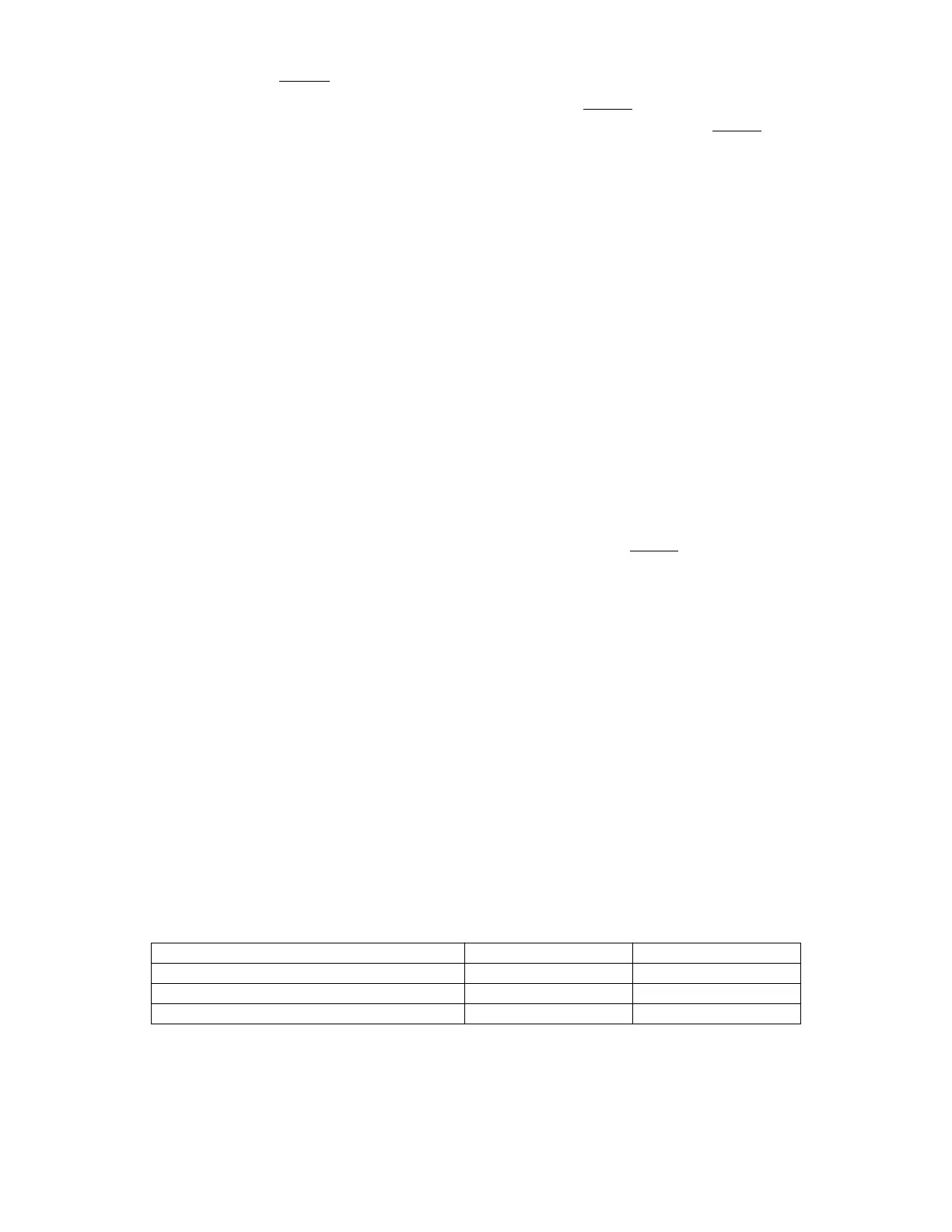

Table 5-4 Polling the BDM Entry Source

Source ATEMP[31:16] ATEMP[15:0]

Double Bus Fault SSW* $FFFF

BGND Instruction $0000 $0001

Hardware Breakpoint $0000 $0000

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...