MC68332 OVERVIEW

USER’S MANUAL 3-9

3.5 Intermodule Bus

The intermodule bus (IMB) is a standardized bus developed to facilitate both design

and operation of modular microcontrollers. It contains circuitry to support exception

processing, address space partitioning, multiple interrupt levels, and vectored inter-

rupts. The standardized modules in the MCU communicate with one another and with

external components through the IMB. The IMB in the MCU uses 24 address and 16

data lines.

3.6 System Memory Map

Figure 3-4 through Figure 3-8 are MCU memory maps. Figure 3-4 shows IMB ad-

dresses of internal registers. Figure 3-5 through Figure 3-8 show system memory

maps that use different external decoding schemes.

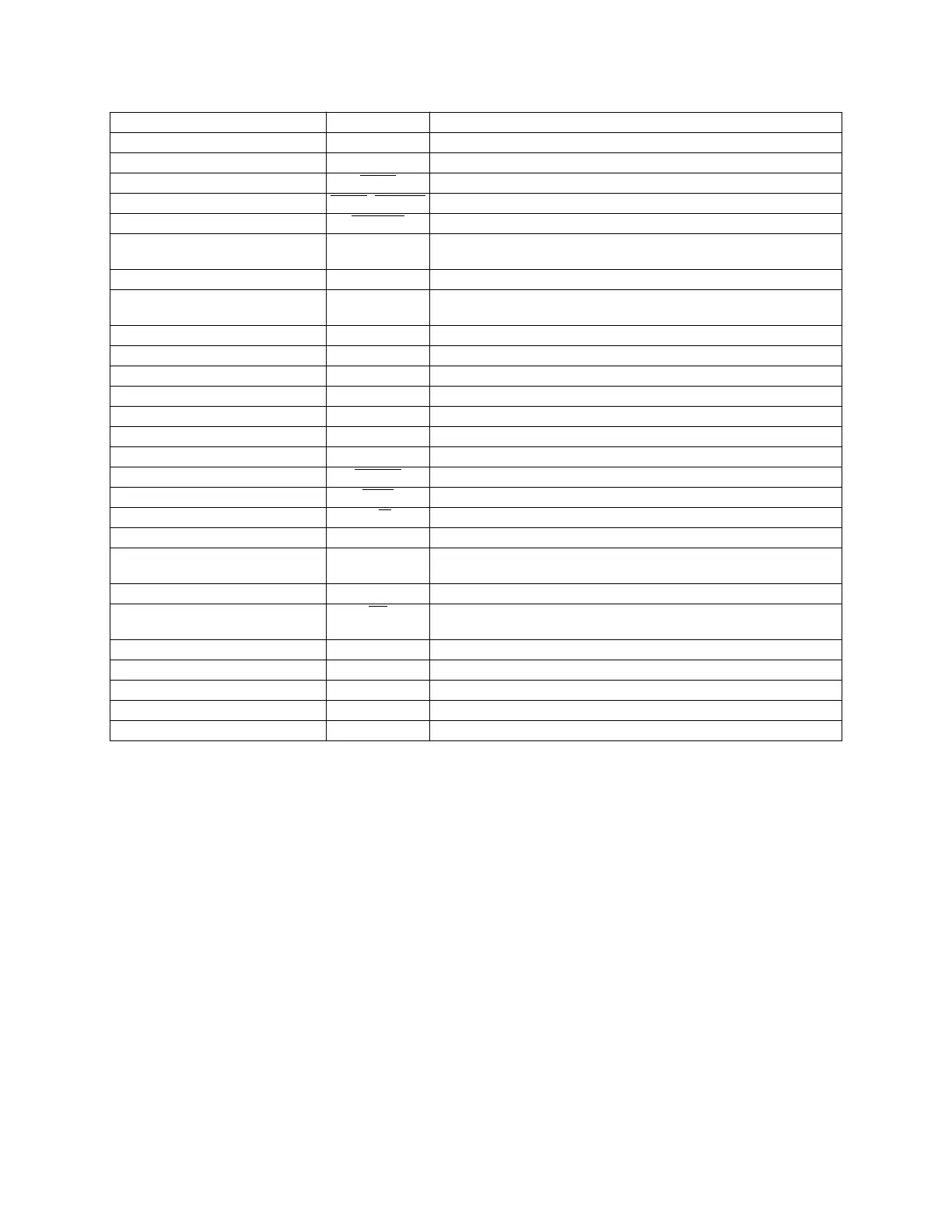

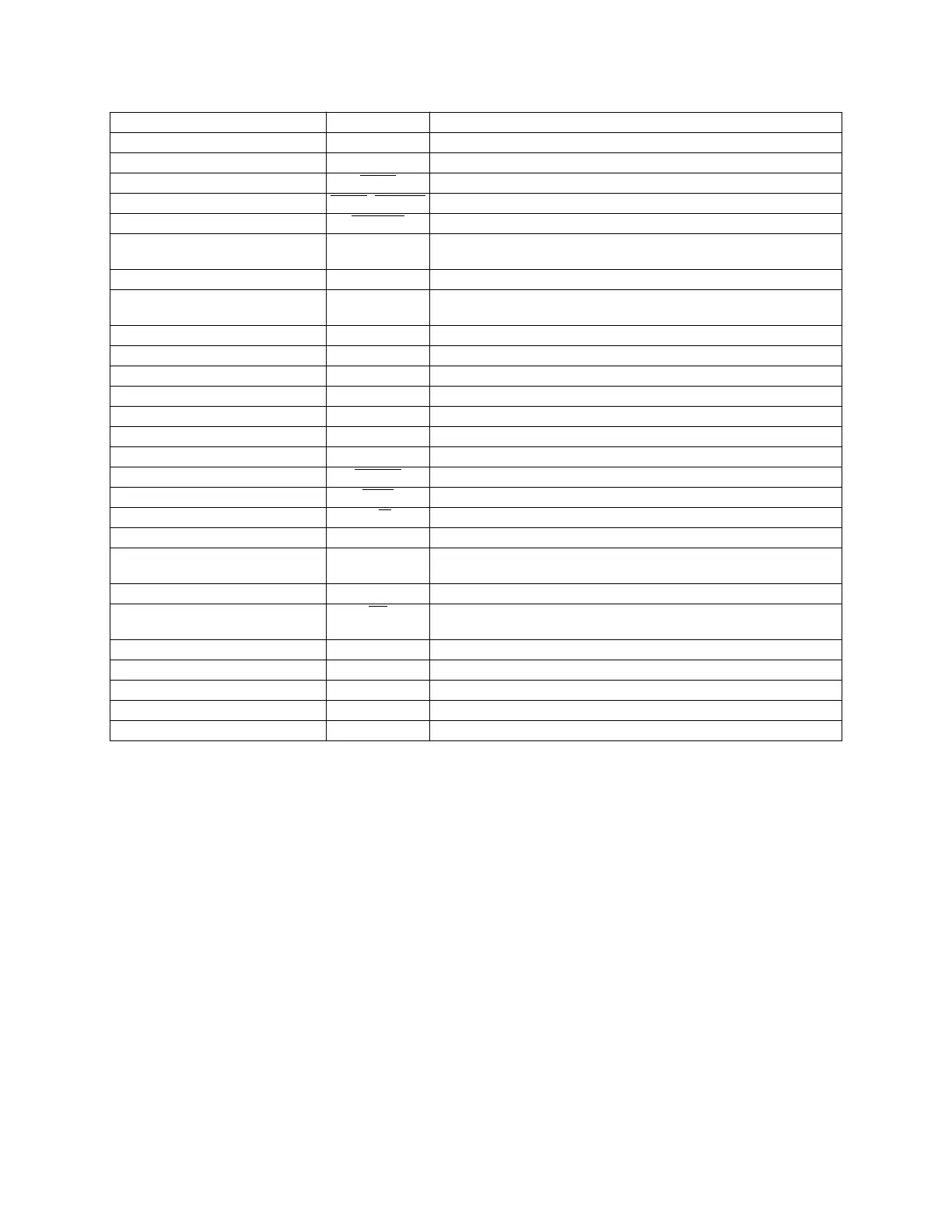

Function Codes FC[2:0] Identify processor state and current address space

Freeze FREEZE Indicates that the CPU has entered background mode

Halt HALT

Suspend external bus activity

Instruction Pipeline IPIPE

, IFETCH Indicate instruction pipeline activity

Interrupt Request Level IRQ[7:1]

Provides an interrupt priority level to the CPU

Master In Slave Out MISO Serial input to QSPI in master mode;

serial output from QSPI in slave mode

Clock Mode Select MODCLK Selects the source and type of system clock

Master Out Slave In MOSI Serial output from QSPI in master mode;

serial input to QSPI in slave mode

Port C PC[6:0] SIM digital output port signals

Auxiliary Timer Clock Input PCLK External clock dedicated to the GPT

Peripheral Chip Select PCS[3:0] QSPI peripheral chip selects

Port E PE[7:0] SIM digital I/O port signals

Port F PF[7:0] SIM digital I/O port signals

Port QS PQS[7:0] QSM digital I/O port signals

Quotient Out QUOT Provides the quotient bit of the polynomial divider

Reset RESET

System reset

Read-Modify-Write Cycle RMC

Indicates an indivisible read-modify-write instruction

Read/Write R/W

Indicates the direction of data transfer on the bus

SCI Receive Data RXD Serial input to the SCI

QSPI Serial Clock SCK Clock output from QSPI in master mode;

clock input to QSPI in slave mode

Size SIZ[1:0] Indicates the number of bytes to be transferred during a bus cycle

Slave Select SS

Causes serial transmission when QSPI is in slave mode;

causes mode fault in master mode

TCR2 Clock T2CLK External clock source for TCR2 counter

TPU Channel Pins TPUCH[15:0] Bidirectional pins associated with TPU channels

Three-State Control TSC Places all output drivers in a high-impedance state

SCI Transmit Data TXD Serial output from the SCI

External Filter Capacitor XFC Connection for external phase-locked loop filter capacitor

Table 3-5 MCU Signal Function (Continued)

Signal Name Mnemonic Function

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...