MC68332 SYSTEM INTEGRATION MODULE

USER’S MANUAL 4-17

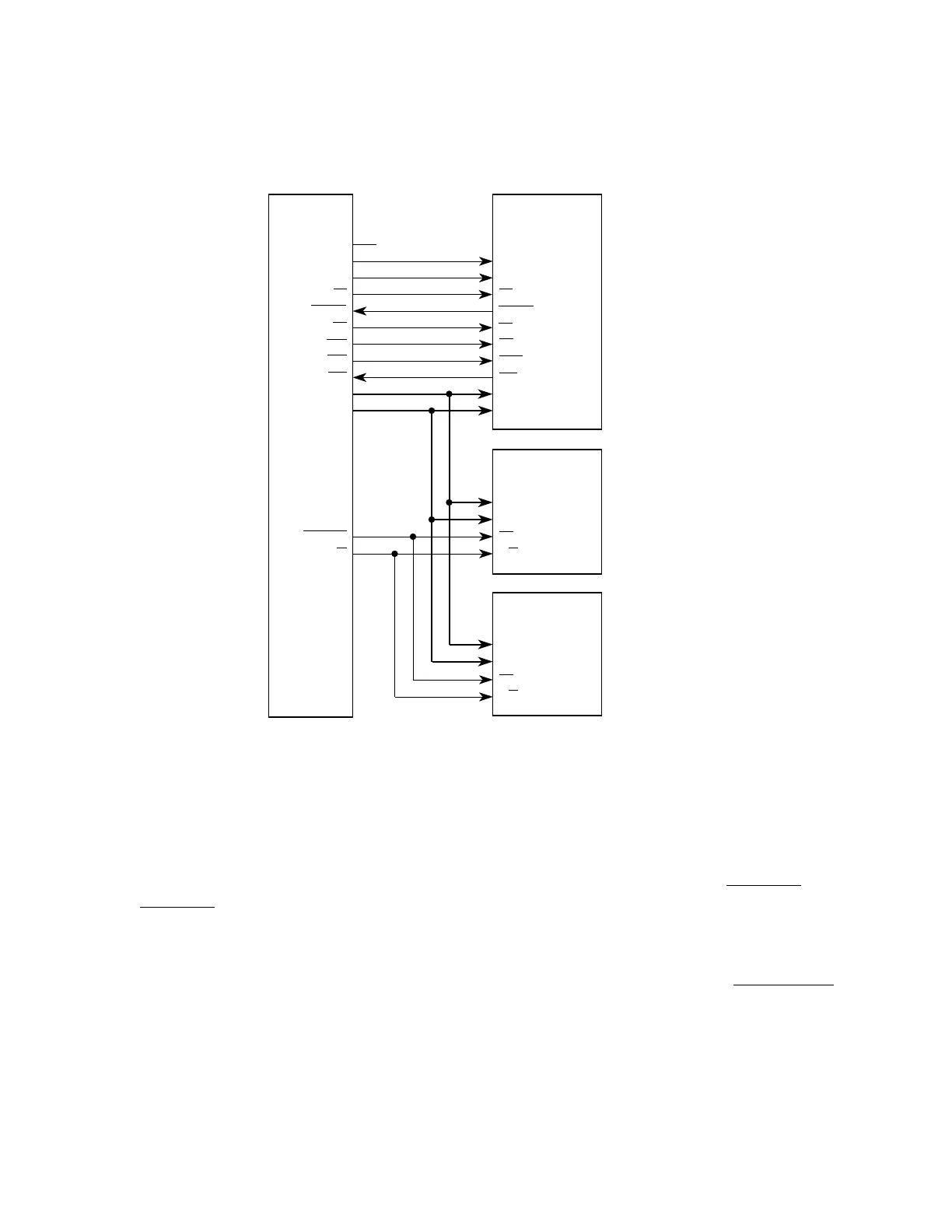

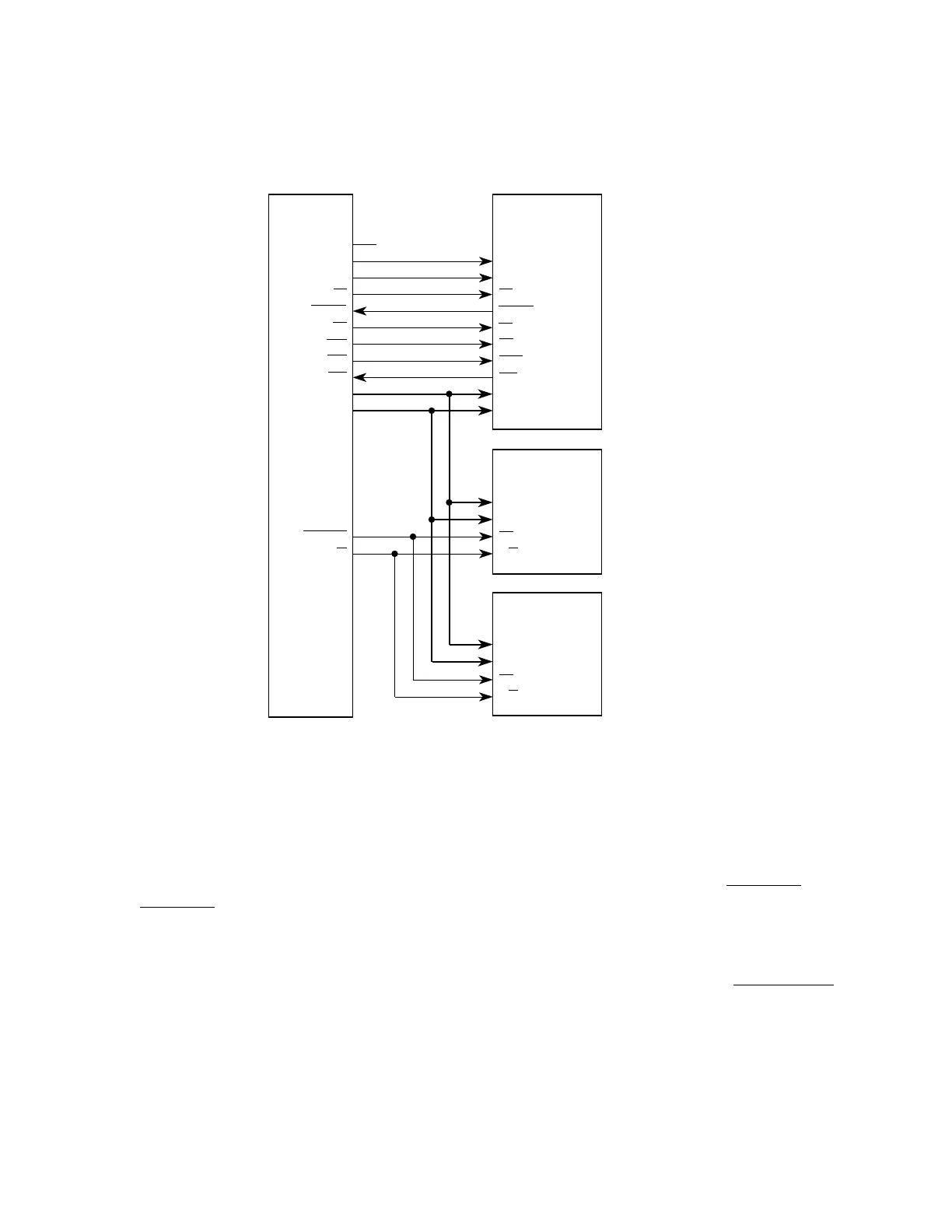

4.4 External Bus Interface

The external bus interface (EBI) transfers information between the internal MCU bus

and external devices. Figure 4-7 shows a basic system with external memory and pe-

ripherals.

Figure 4-7 MCU Basic System

The external bus has 24 address lines and 16 data lines. The EBI provides dynamic

sizing between 8-bit and 16-bit data accesses. It supports byte, word, and long-word

transfers. Ports are accessed through the use of asynchronous cycles controlled by

the data transfer (SIZ1 and SIZ0) and data size acknowledge pins (DSACK1

and

DSACK0

). Multiple bus cycles may be required for a transfer to or from an 8-bit port.

The maximum number of bits transferred during an access is referred to as port width.

Widths of eight and sixteen bits can be accessed by asynchronous bus cycles con-

trolled by the data size (SIZ[1:0]) and the data and size acknowledge (DSACK[1:0]

)

signals. Multiple bus cycles may be required for a dynamically-sized transfer.

To add flexibility and minimize the necessity for external logic, MCU chip-select logic

can be synchronized with EBI transfers. Refer to 4.8 Chip Selects for more informa-

tion.

32 EXAMPLE SYS BLOCK

ADDR[23:0]

SIZ

CLKOUT

AS

FC

DSACK

DS

R/W

DATA[15:0]

CS3

CS5

IRQ

CSBOOT

ADDR[15:0]

SIZ

CLK

DSACK

AS

DS

CS

DATA[15:0]

IACK

IRQ

ADDR[23:0]

DATA[15:8]

CS

R/W

MEMORY

ADDR[23:0]

DATA[7:0]

CS

R/W

MEMORY

MCU

ASYNC BUS

PERIPHERAL

1

2

2

2

1. Can be decoded to provide additional address space.

2. Varies depending upon peripheral memory size.

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...