SYSTEM INTEGRATION MODULE MC68332

4-38 USER’S MANUAL

4.6.2 Reset Control Logic

SIM reset control logic determines the cause of a reset, synchronizes reset assertion

if necessary to the completion of the current bus cycle, and asserts the appropriate re-

set lines. Reset control logic can drive four different internal signals.

1. EXTRST (external reset) drives the external reset pin.

2. CLKRST (clock reset) resets the clock module.

3. MSTRST (master reset) goes to all other internal circuits.

4. SYSRST (system reset) indicates to internal circuits that the CPU has executed

a RESET instruction.

All resets are gated by CLKOUT. Resets are classified as synchronous or asynchro-

nous. An asynchronous reset can occur on any CLKOUT edge. Reset sources that

cause an asynchronous reset usually indicate a catastrophic failure; thus the reset

control logic responds by asserting reset to the system immediately. (A system reset,

however, caused by the CPU32 RESET instruction, is asynchronous but does not in-

dicate any type of catastrophic failure).

Synchronous resets are timed (CLKOUT) to occur at the end of bus cycles. The inter-

nal bus monitor is automatically enabled for synchronous resets. When a bus cycle

does not terminate normally, the bus monitor terminates it.

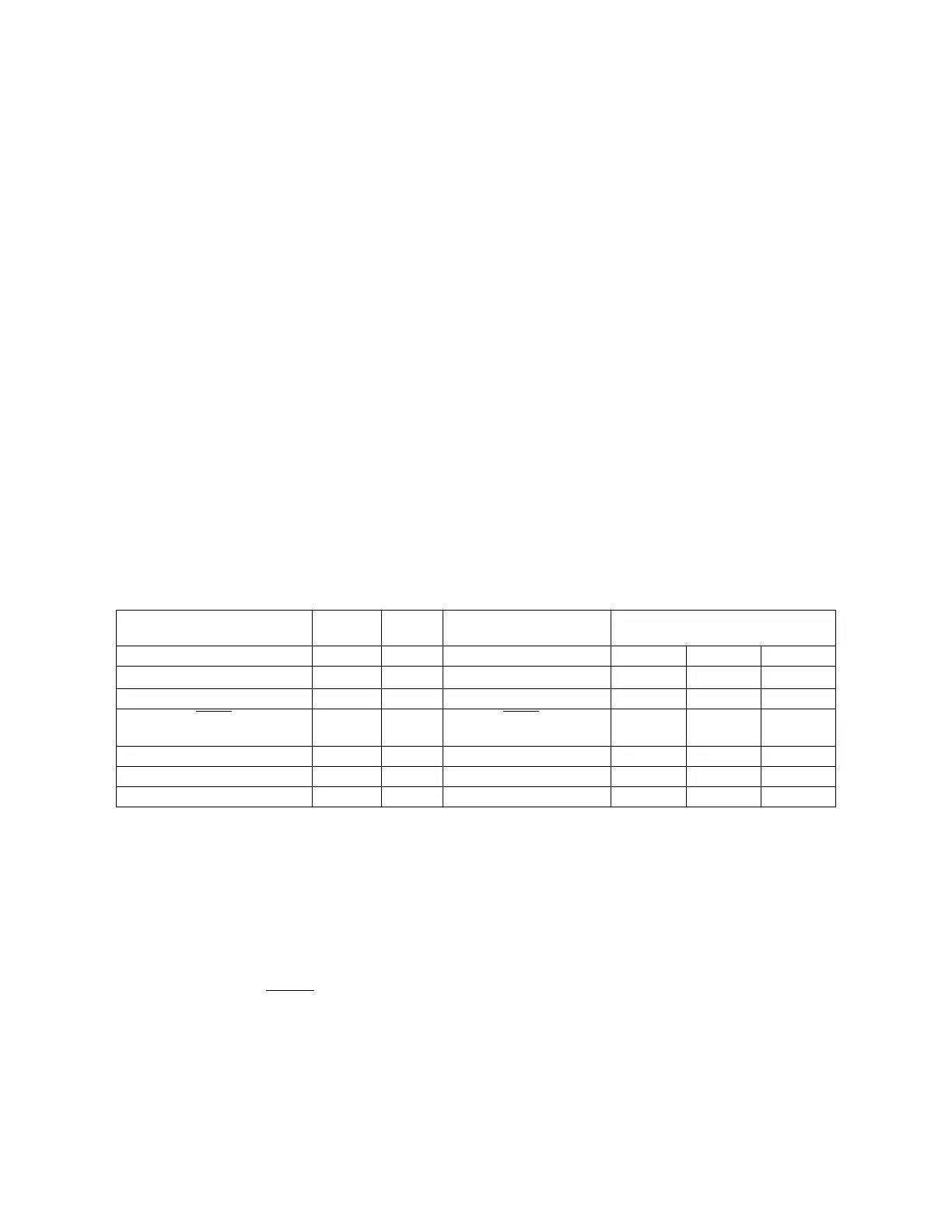

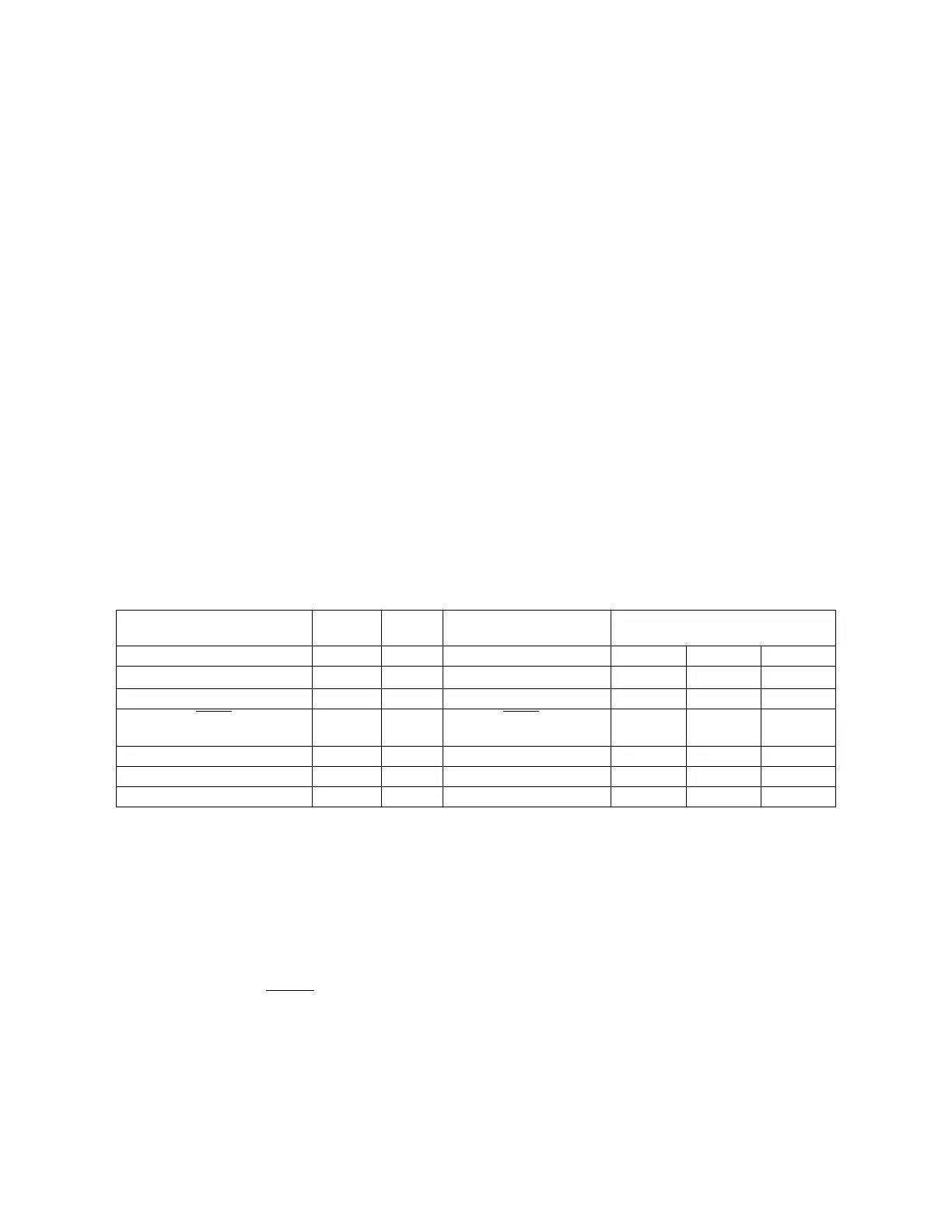

Refer to Table 4-15 for a summary of reset sources.

Internal single byte or aligned word writes are guaranteed valid for synchronous re-

sets. External writes are also guaranteed to complete, provided the external configu-

ration logic on the data bus is conditioned as shown in Figure 4-13.

4.6.3 Reset Mode Selection

The logic states of certain data bus pins during reset determine SIM operating config-

uration. In addition, the state of the MODCLK pin determines system clock source and

the state of the BKPT

pin determines what happens during subsequent breakpoint as-

sertions. Table 4-16 is a summary of reset mode selection options.

Table 4-15 Reset Source Summary

Type Source Timing Cause Reset Lines Asserted by

Controller

External External Synch External Signal MSTRST CLKRST EXTRST

Power Up EBI Asynch V

DD

MSTRST CLKRST EXTRST

Software Watchdog Monitor Asynch Time Out MSTRST CLKRST EXTRST

HALT

Monitor Asynch Internal HALT Assertion

(e.g. Double Bus Fault)

MSTRST CLKRST EXTRST

Loss of Clock Clock Synch Loss of Reference MSTRST CLKRST EXTRST

Test Test Synch Test Mode MSTRST — EXTRST

System CPU32 Asynch RESET Instruction — — EXTRST

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...