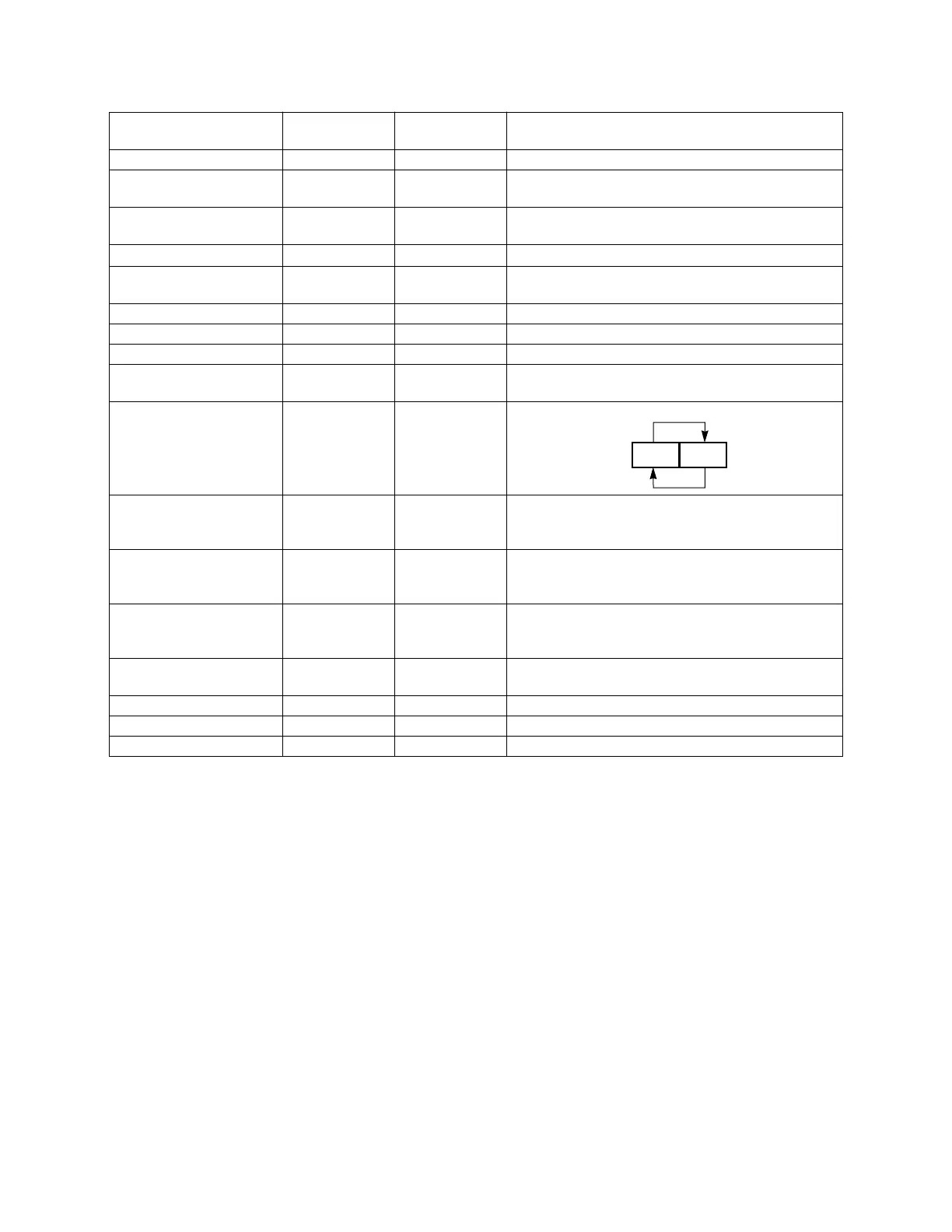

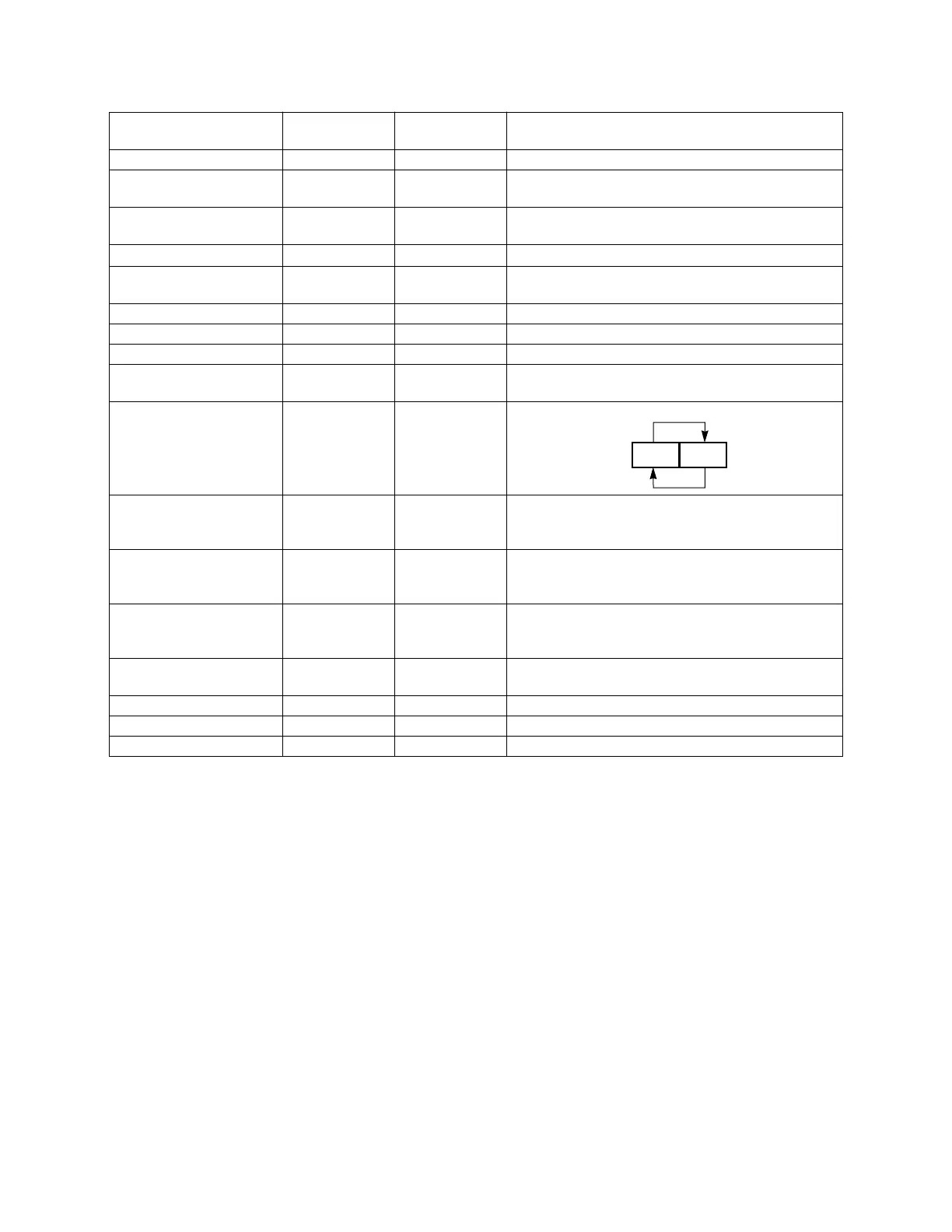

CENTRAL PROCESSING UNIT MC68332

5-12 USER’S MANUAL

NOTE:

1. Privileged instruction.

5.8.1 M68000 Family Compatibility

It is the philosophy of the M68000 family that all user-mode programs can execute un-

changed on a more advanced processor, and supervisor-mode programs and excep-

tion handlers should require only minimal alteration.

The CPU32 can be thought of as an intermediate member of the M68000 Family. Ob-

ject code from an MC68000 or MC68010 may be executed on the CPU32, and many

of the instruction and addressing mode extensions of the MC68020 are also support-

ed. Refer to the CPU32 reference manual for a detailed comparison of the CPU32 and

MC68020 instruction set.

RTR none none (SP) ⇒ CCR; SP + 2 ⇒ SP; (SP) ⇒ PC;

SP + 4 ⇒ SP

RTS none none (SP) ⇒ PC; SP + 4 ⇒ SP

SBCD Dn, Dn

– (An), – (An)

8

8

Destination

10

– Source

10

– X ⇒ Destination

Scc Í 8 If condition true, then destination bits are set to 1;

else, destination bits are cleared to 0

STOP

1

#<data> 16 Data ⇒ SR; STOP

SUB <ea>, Dn

Dn, <ea>

8, 16, 32 Destination – Source ⇒ Destination

SUBA <ea>, An 16, 32 Destination – Source ⇒ Destination

SUBI #<data>, <ea> 8, 16, 32 Destination – Data ⇒ Destination

SUBQ #<data>, <ea> 8, 16, 32 Destination – Data ⇒ Destination

SUBX Dn, Dn

– (An), – (An)

8, 16, 32

8, 16, 32

Destination – Source – X ⇒ Destination

SWAP Dn 16

TBLS/TBLU <ea>, Dn

Dym : Dyn, Dn

8, 16, 32 Dyn – Dym ⇒ Temp

(Temp * Dn [7 : 0]) ⇒ Temp

(Dym * 256) + Temp ⇒ Dn

TBLSN/TBLUN <ea>, Dn

Dym : Dyn, Dn

8, 16, 32 Dyn – Dym ⇒ Temp

(Temp * Dn [7 : 0]) / 256 ⇒ Temp

Dym + Temp ⇒ Dn

TRAP #<data> none SSP – 2 ⇒ SSP; format/vector offset ⇒ (SSP);

SSP – 4 ⇒ SSP; PC ⇒ (SSP); SR ⇒ (SSP);

vector address ⇒ PC

TRAPcc none

#<data>

none

16, 32

If cc true, then TRAP exception

TRAPV none none If V set, then overflow TRAP exception

TST Í 8, 16, 32 Source – 0, to set condition codes

UNLK An 32 An ⇒ SP; (SP) ⇒ An, SP + 4 ⇒ SP

Table 5-1 Instruction Set Summary

MSW LSW

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...