QUEUED SERIAL MODULE MC68332

6-4 USER’S MANUAL

the corresponding pin to general-purpose I/O; setting a bit assigns the pin to the QSPI.

PQSPAR does not affect operation of the SCI.

The port QS data direction register (DDRQS) determines whether pins are inputs or

outputs. Clearing a bit makes the corresponding pin an input; setting a bit makes the

pin an output. DDRQS affects both QSPI function and I/O function. DDQS1 deter-

mines the direction of the TXD pin only when the SCI transmitter is disabled. When the

SCI transmitter is enabled, the TXD pin is an output. PQSPAR and DDRQS are 8-bit

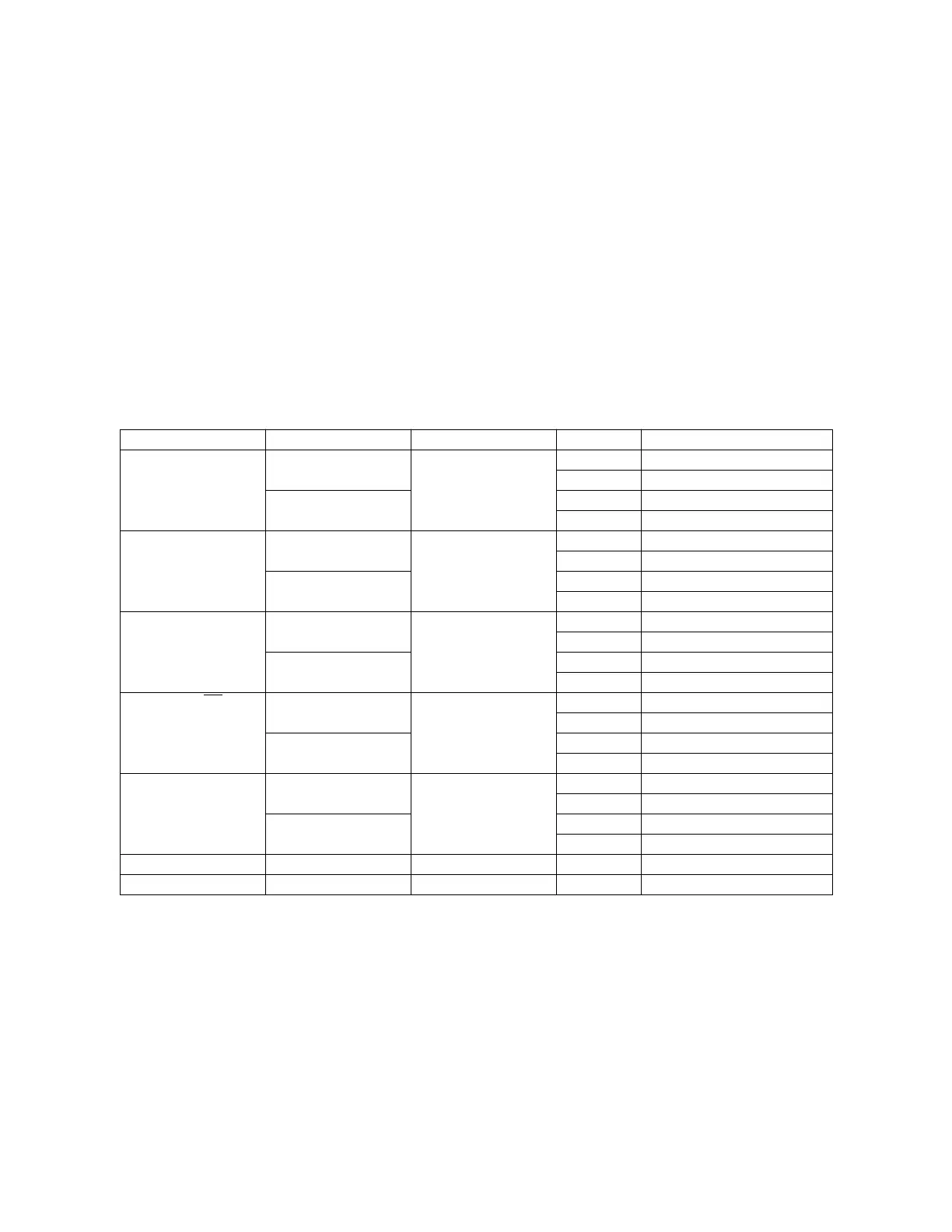

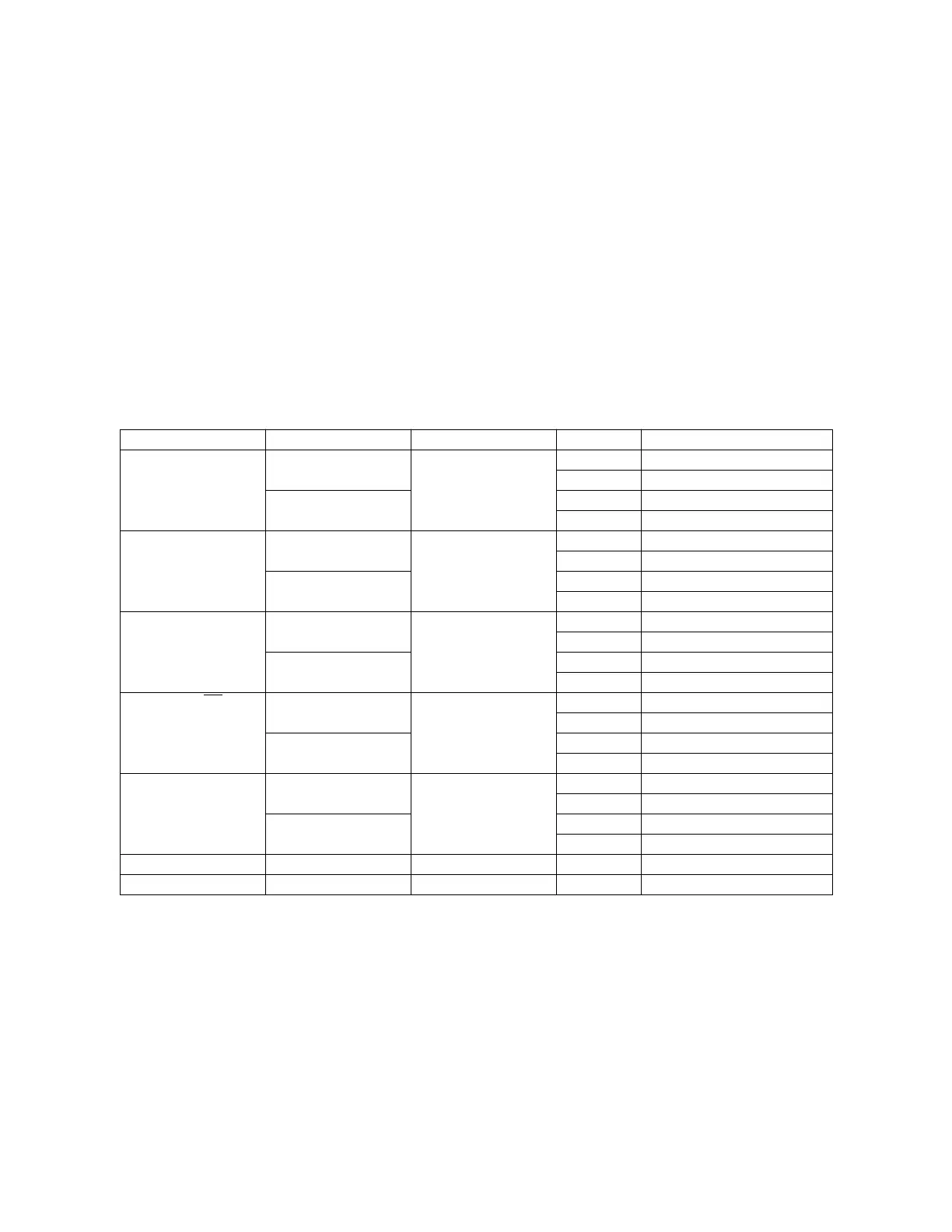

registers located at the same word address. Table 6-1 is a summary of QSM pin func-

tions.

The port QS data register (PORTQS) latches I/O data. Writes to PORTQS drive pins

defined as outputs. PORTQS reads return data present on the pins when the read is

made. To avoid driving undefined data, first write PORTQS, then configure DDRQS.

6.3 Queued Serial Peripheral Interface

The queued serial peripheral interface (QSPI) communicates with external devices

through a synchronous serial bus. The QSPI is fully compatible with SPI systems

found on other Freescale products, but has enhanced capabilities. The QSPI can per-

NOTES:

1. PQS2 is a digital I/O pin unless the SPI is enabled (SPE in SPCR1 set), in which case it becomes the SPI

serial clock SCK.

2. PQS7 is a digital I/O pin unless the SCI transmitter is enabled (TE in SCCR1 set), in which case it becomes

SCI serial output TXD and DDRQS has no effect.

Table 6-1 QSM Pin Function

QSM Pin Mode DDRQS Bit Bit State Pin Function

MISO Master DDQS0 0 Serial Data Input to QSPI

1 Disables Data Input

Slave 0 Disables Data Output

1 Serial Data Output from QSPI

MOSI Master DDQS1 0 Disables Data Output

1 Serial Data Output from QSPI

Slave 0 Serial Data Input to QSPI

1 Disables Data Input

SCK

1

Master DDQS2 0 Disables Clock Output

1 Clock Output from QSPI

Slave 0 Clock Input to QSPI

1 Disables Clock Input

PCS0/SS

Master DDQS3 0 Assertion Causes Mode Fault

1 Chip-Select Output

Slave 0 QSPI Slave Select Input

1 Disables Select Input

PCS[3:1] Master DDQS[4:6] 0 Disables Chip-Select Output

1 Chip-Select Output

Slave 0 Inactive

1 Inactive

TXD

2

Transmit DDQS7 X Serial Data Output from SCI

RXD Receive None NA Serial Data Input to SCI

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...