MC68332 REGISTER SUMMARY

USER’S MANUAL D-23

PF — Parity Error

0 = No parity error on the received data

1 = Parity error occurred on the received data.

D.4.7 SCDR — SCI Data Register $YFFC0E

SCDR consists of two data registers located at the same address. RDR is a read-only

register that contains data received by the SCI serial interface. Data comes into the

receive serial shifter and is transferred to RDR. TDR is a write-only register that con-

tains data to be transmitted. Data is first written to TDR, then transferred to the transmit

serial shifter, where additional format bits are added before transmission. R[7:0]/T[7:0]

contain either the first eight data bits received when SCDR is read, or the first eight

data bits to be transmitted when SCDR is written. R8/T8 are used when the SCI is con-

figured for nine-bit operation. When the SCI is configured for eight-bit operation, R8/

T8 have no meaning or effect.

D.4.8 PORTQS — Port QS Data Register $YFFC15

PORTQS latches I/O data. Writes drive pins defined as outputs. Reads return data

present on the pins. To avoid driving undefined data, first write a byte to PORTQS,

then configure DDRQS.

D.4.9 PQSPAR — PORT QS Pin Assignment Register $YFFC16

DDRQS — PORT QS Data Direction Register $YFFC17

Clearing a bit in PQSPAR assigns the corresponding pin to general-purpose I/O; set-

ting a bit assigns the pin to the QSPI. PQSPAR does not affect operation of the SCI.

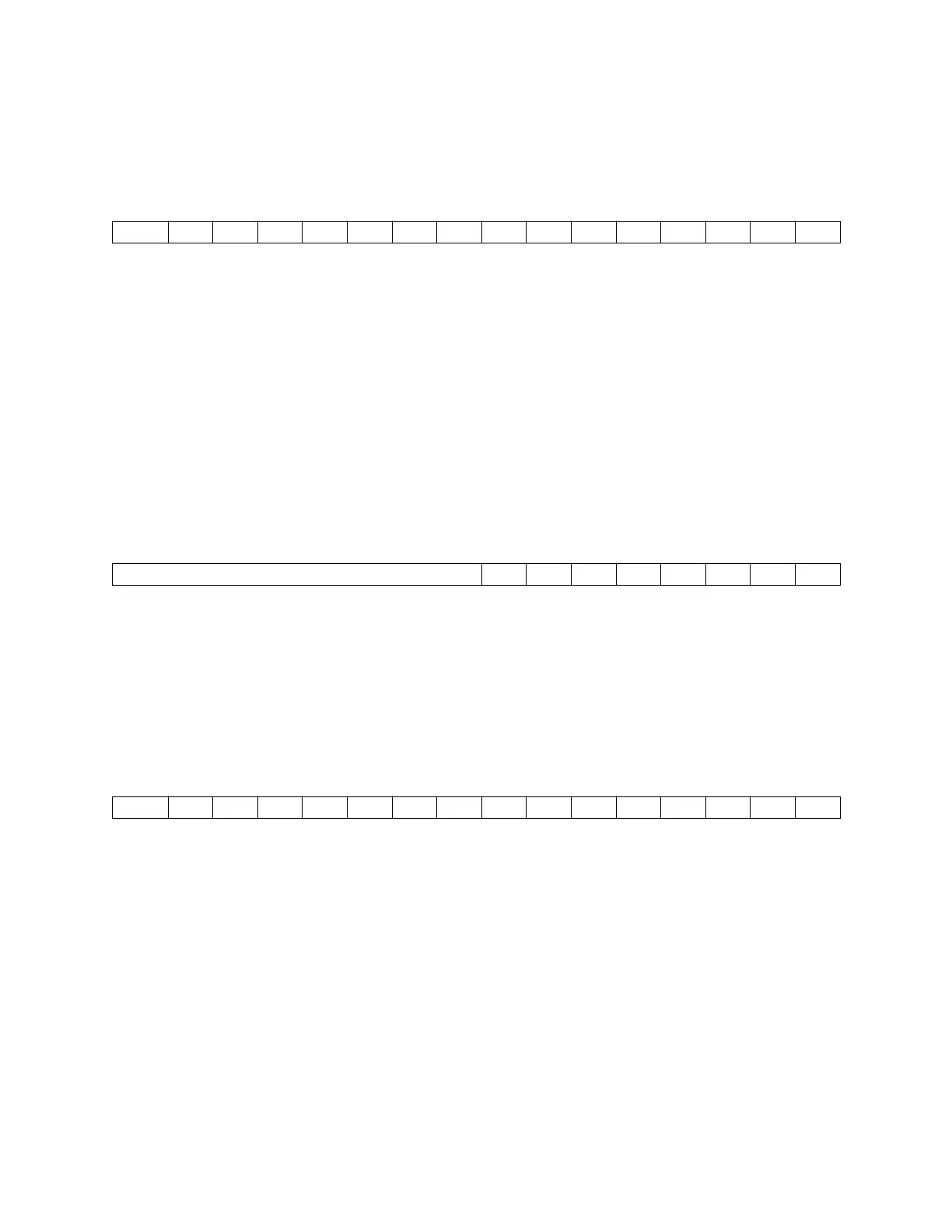

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 R8/T8 R7/T7 R6/T6 R5/T5 R4/T4 R3/T3 R2/T2 R1/T1 R0/T0

RESET:

0 0 0 0 0 0 0 U U U U U U U U U

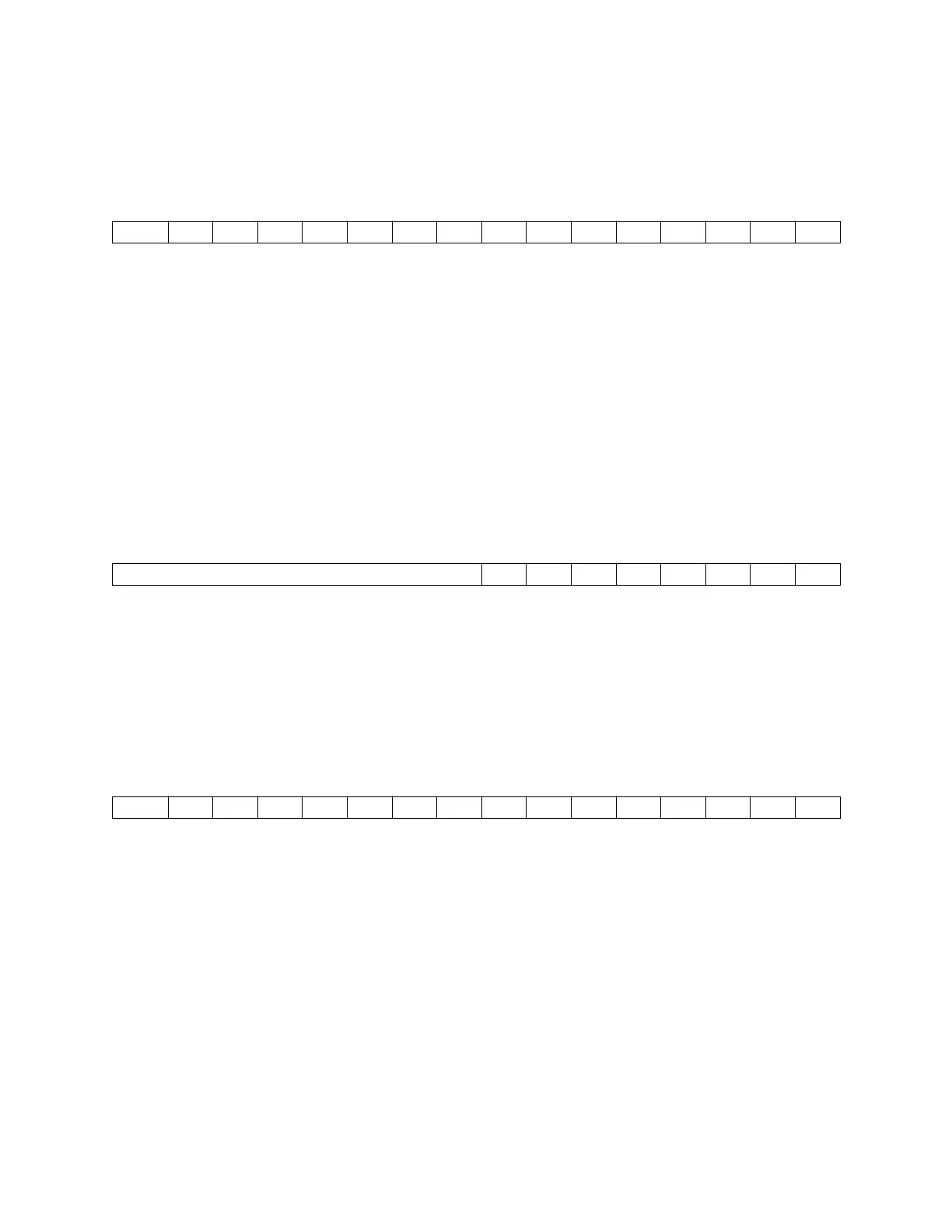

15 8 7 6 5 4 3 2 1 0

NOT USED PQS7 PQS6 PQS5 PQS4 PQS3 PQS2 PQS1 PQS0

RESET:

0 0 0 0 0 0 0 0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0

PQSPA6 PQSPA5 PQSPA4 PQSPA3

0

PQSPA1 PQSPA0

DDQS7 DDQS6 DDQS5 DDQS4 DDQS3 DDQS2 DDQS1 DDQS0

RESET:

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...