SYSTEM INTEGRATION MODULE MC68332

4-56 USER’S MANUAL

During a CPU space cycle, bits [15:3] of the appropriate base register must be config-

ured to match ADDR[23:11], as the address is compared to an address generated by

the CPU.

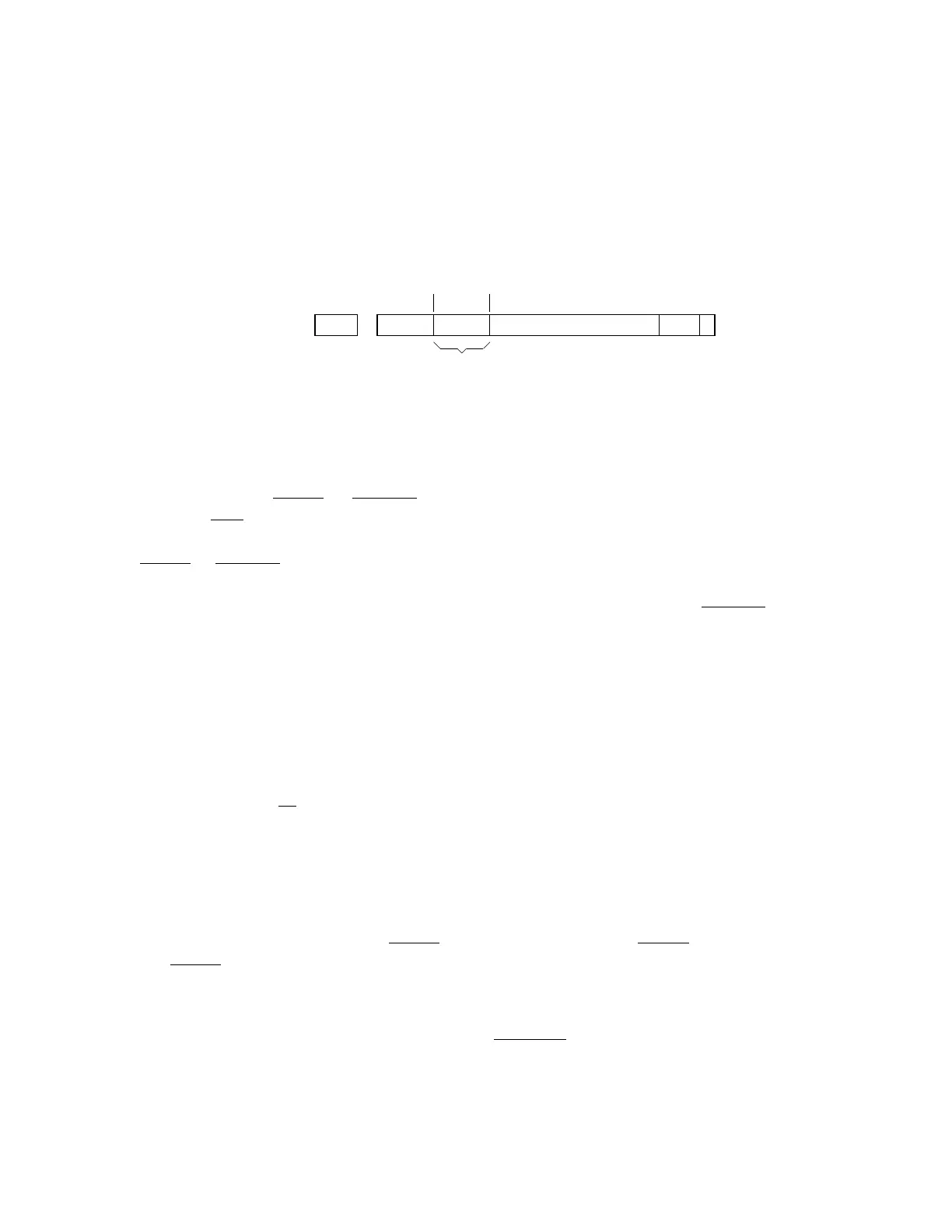

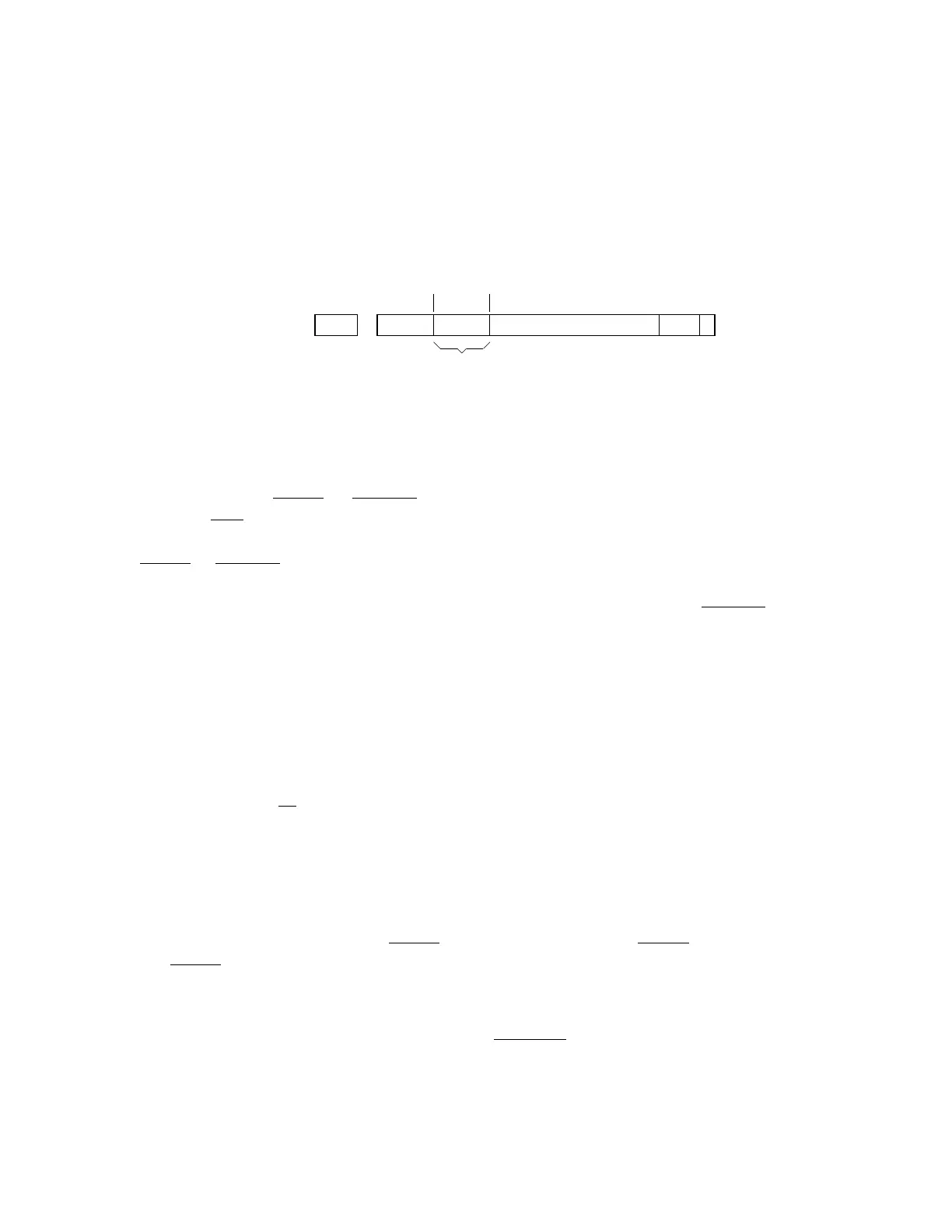

Figure 4-19 shows CPU space encoding for an interrupt acknowledge cycle. FC[2:0]

are set to %111, designating CPU space access. ADDR[3:1] indicate interrupt priority,

and the space type field (ADDR[19:16]) is set to %1111, the interrupt acknowledge

code. The rest of the address lines are set to one.

Figure 4-19 CPU Space Encoding for Interrupt Acknowledge

Because address match logic functions only after the EBI transfers an interrupt ac-

knowledge cycle to the external address bus following IARB contention, chip-select

logic generates AVEC

or DSACK signals only in response to interrupt requests from

external IRQ

pins. If an internal module makes an interrupt request of a certain priority,

and the chip-select base address and option registers are programmed to generate

AVEC

or DSACK signals in response to an interrupt acknowledge cycle for that priority

level, chip-select logic does not respond to the interrupt acknowledge cycle, and the

internal module supplies a vector number and generates an internal DSACK

signal to

terminate the cycle.

Perform the following operations before using a chip select to generate an interrupt ac-

knowledge signal.

1. Program the base address field to all ones.

2. Program block size to no more than 64 Kbytes, so that the address comparator

checks ADDR[19:16] against the corresponding bits in the base address regis-

ter. (The CPU32 places the CPU32 space type on ADDR[19:16].)

3. Set the R/W

field to read only. An interrupt acknowledge cycle is performed as

a read cycle.

4. Set the BYTE field to lower byte when using a 16-bit port, as the external vector

for a 16-bit port is fetched from the lower byte. Set the BYTE field to upper byte

when using an 8-bit port.

If an interrupting device does not provide a vector number, an autovector acknowledge

must be generated. Asserting AVEC

, either by asserting the AVEC pin or by generat-

ing AVEC

internally using the chip-select option register, terminates the bus cycle.

4.8.4 Chip-Select Reset Operation

The least significant bits of each of the 2-bit CS[10:0] pin assignment fields in CSPAR0

and CSPAR1 each have a reset value of one. The reset values of the most significant

bits of each field are determined by the states of DATA[7:1] during reset. There are

CPU SPACE IACK TIM

11111111111111111111 1111

LEVEL

19 1623

FUNCTION

CODE

20 0

CPU SPACE

TYPE FIELD

ADDRESS BUS

INTERRUPT

ACKNOWLEDGE

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...