MC68332 SYSTEM INTEGRATION MODULE

USER’S MANUAL 4-15

4.3.3 External Bus Clock

The state of the external clock division bit (EDIV) in SYNCR determines clock rate for

the external bus clock signal (ECLK) available on pin ADDR23. ECLK is a bus clock

for MC6800 devices and peripherals. ECLK frequency can be set to system clock fre-

quency divided by eight or system clock frequency divided by sixteen. The clock is en-

abled by the CS10

field in chip select pin assignment register 1 (CSPAR1). ECLK

operation during low-power stop is described in the following paragraph. Refer to 4.8

Chip Selects for more information about the external bus clock.

4.3.4 Low-Power Operation

Low-power operation is initiated by the CPU32. To reduce power consumption selec-

tively, the CPU can set the STOP bits in each module configuration register. To mini-

mize overall microcontroller power consumption, the CPU can execute the LPSTOP

instruction, which causes the SIM to turn off the system clock.

When individual module STOP bits are set, clock signals inside each module are

turned off, but module registers are still accessible.

When the CPU executes LPSTOP, a special CPU space bus cycle writes a copy of

the current interrupt mask into the clock control logic. The SIM brings the MCU out of

low-power operation when either an interrupt of higher priority than the stored mask or

a reset occurs. Refer to 4.5.4.2 LPSTOP Broadcast Cycle and SECTION 5 CEN-

TRAL PROCESSING UNIT for more information.

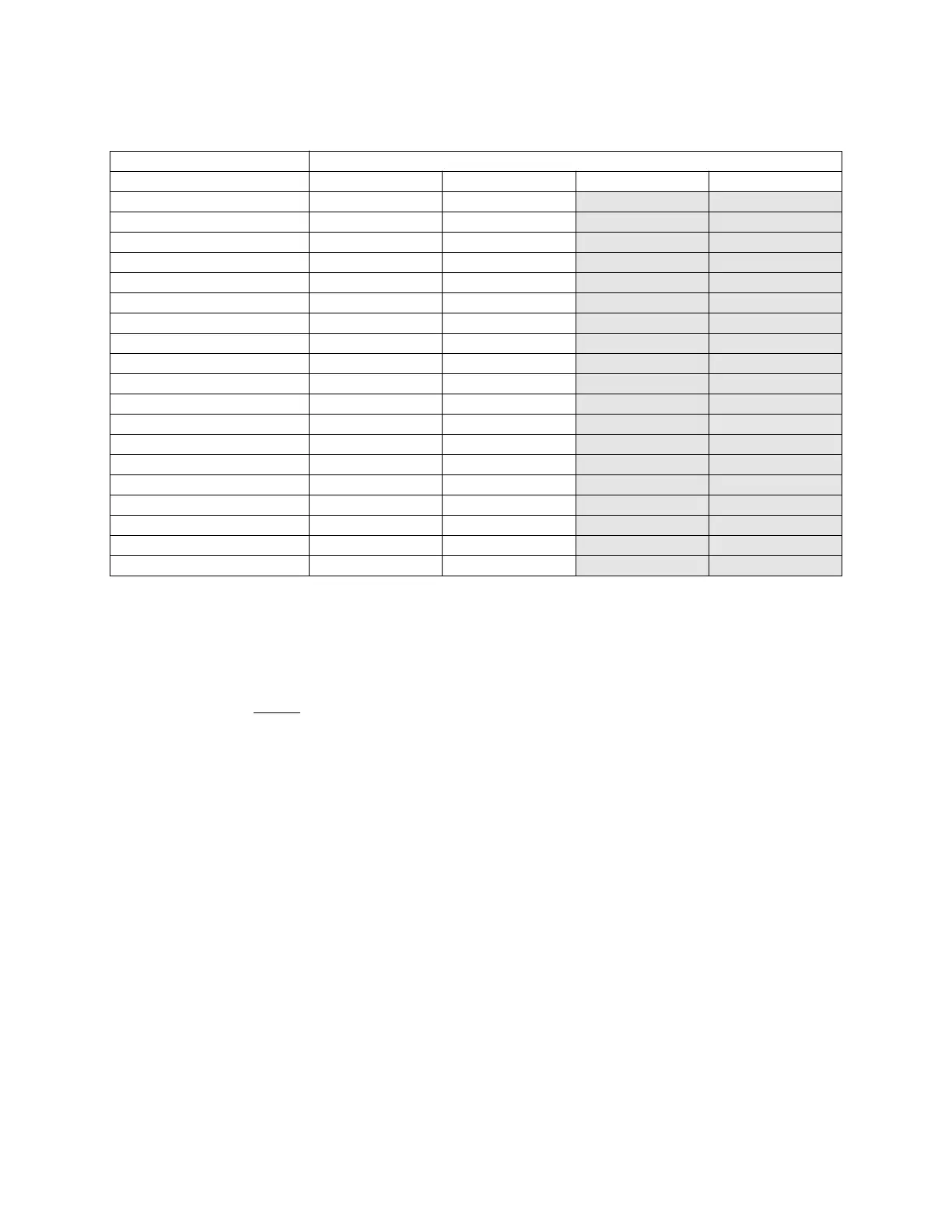

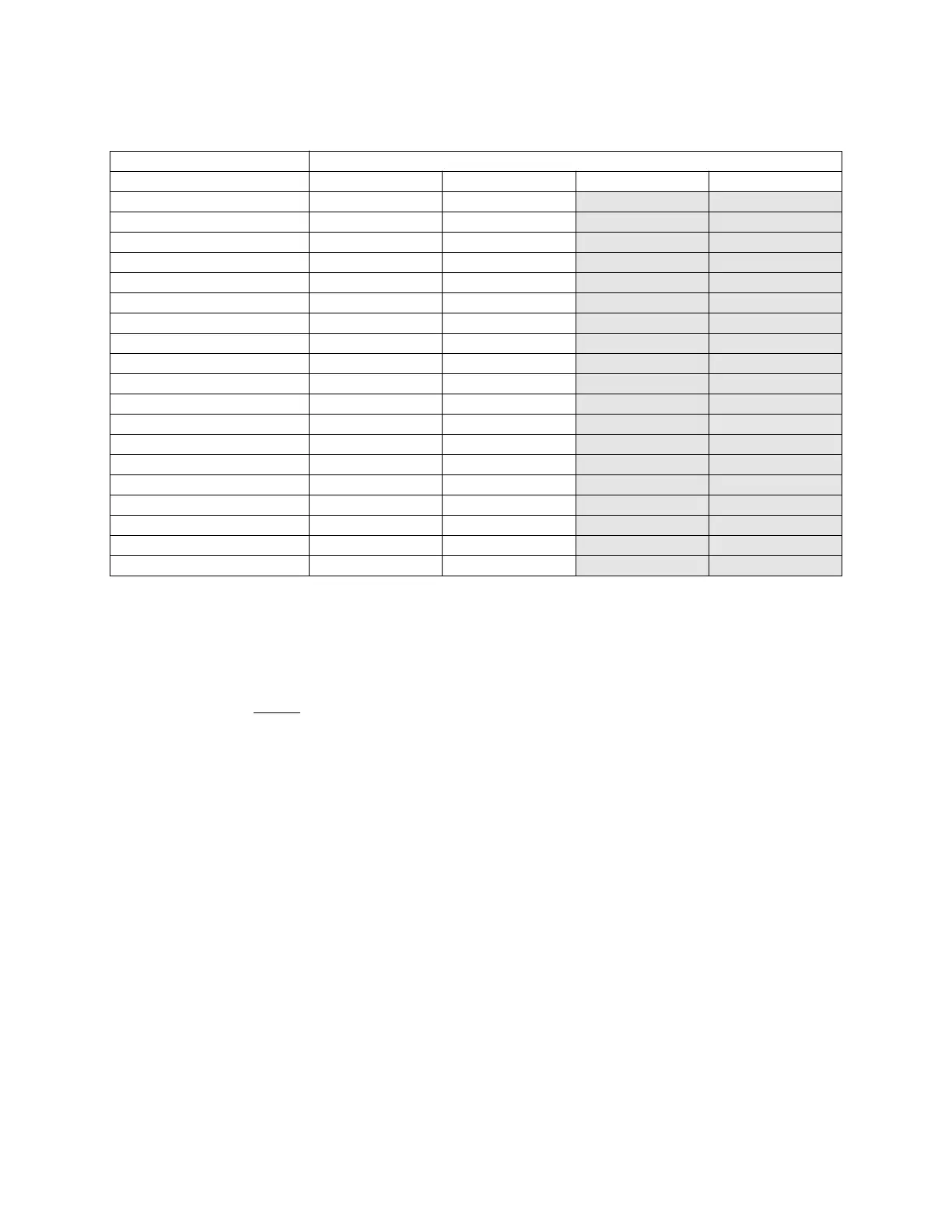

101101 6029 12059 24117 48234

101110 6160 12321

24642 49283

101111 6291 12583

25166 50332

110000 6423 12845

25690 51380

110001 6554 13107

26214 52428

110010 6685 13369

26739 53477

110011 6816 13631

27263 54526

110100 6947 13894

27787 55575

110101 7078 14156

28312 56623

110110 7209 14418

28836 57672

110111 7340 14680

29360 58720

111000 7471 14942

2988 59769

111001 7602 15204

30409 60817

111010 7733 15466

30933 61866

111011 7864 15729

31457 62915

111100 7995 15991

31982 63963

111101 8126 16253

32506 65011

111110 8258 16515

33030 66060

111111 8389 16777

33554 67109

Table 4-8 System Frequencies from 32.768–kHz Reference (Continued)

To obtain clock frequency in kilohertz, find counter modulus in the left column, then multiply reference frequency by value

in appropriate prescaler cell.

Modulus Prescaler

Y [W:X] = 00 [W:X] = 01 [W:X] = 10 [W:X] = 11

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...