SYSTEM INTEGRATION MODULE MC68332

4-22 USER’S MANUAL

4.4.4 Misaligned Operands

CPU32 architecture uses a basic operand size of 16 bits. An operand is misaligned

when it overlaps a word boundary. This is determined by the value of ADDR0. When

ADDR0 = 0 (an even address), the address is on a word and byte boundary. When

ADDR0 = 1 (an odd address), the address is on a byte boundary only. A byte operand

is aligned at any address; a word or long-word operand is misaligned at an odd ad-

dress.

The largest amount of data that can be transferred by a single bus cycle is an aligned

word. If the MCU transfers a long-word operand through a 16-bit port, the most signif-

icant operand word is transferred on the first bus cycle and the least significant oper-

and word is transferred on a following bus cycle.

4.4.5 Operand Transfer Cases

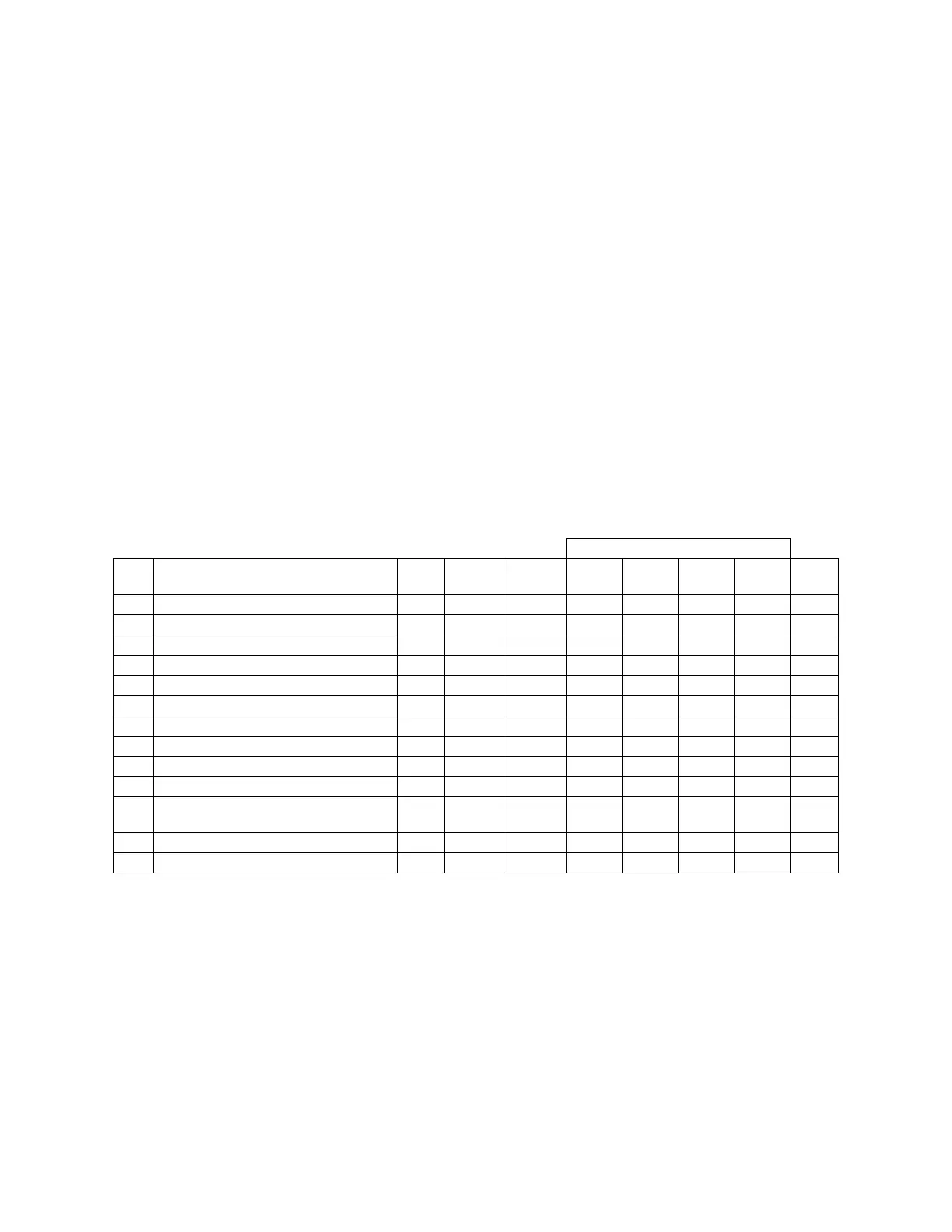

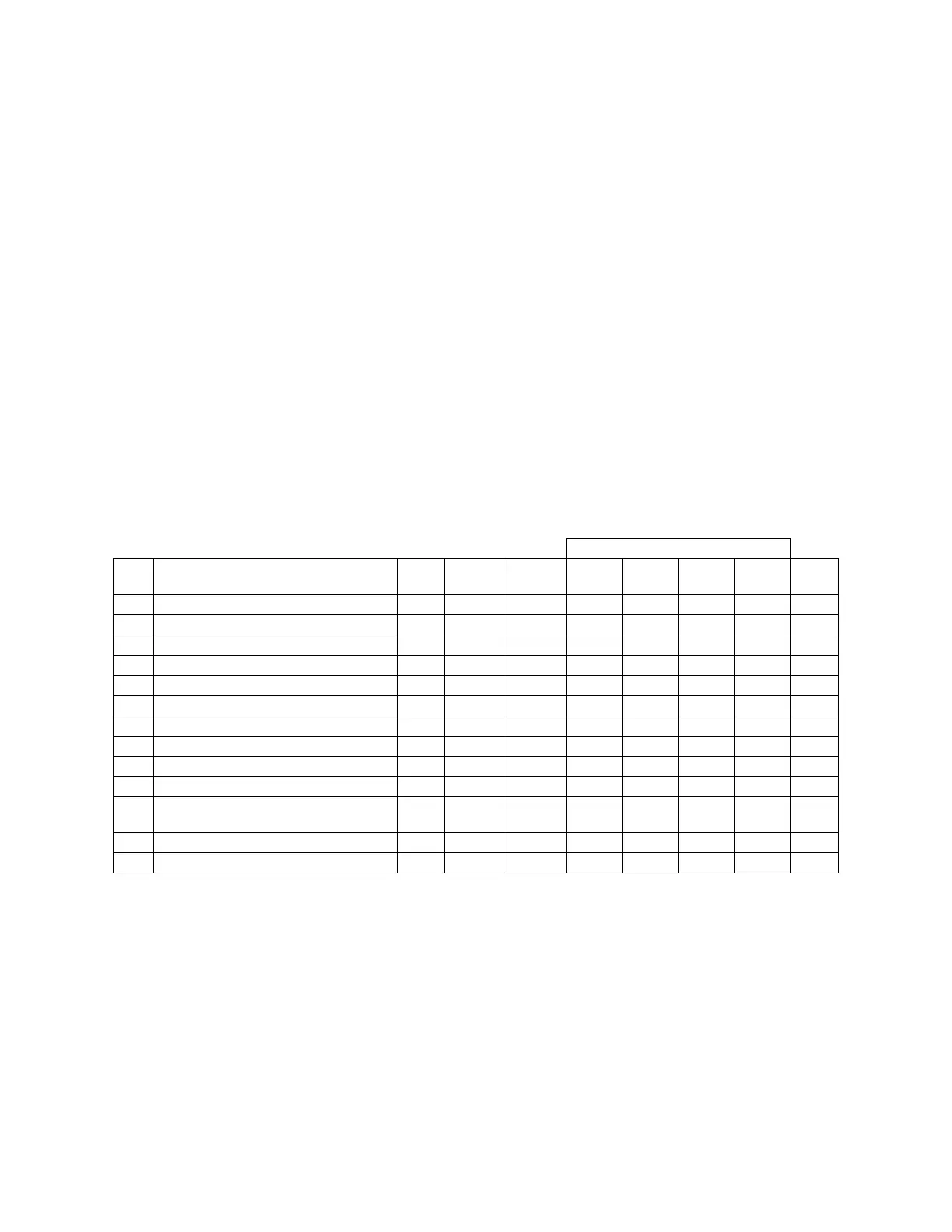

Table 4-13 is a summary of how operands are aligned for various types of transfers.

OPn entries are portions of a requested operand that are read or written during a bus

cycle and are defined by SIZ1, SIZ0, and ADDR0 for that bus cycle. The following

paragraphs discuss all the allowable transfer cases in detail.

4.5 Bus Operation

Internal microcontroller modules are typically accessed in two system clock cycles,

with no wait states. Regular external bus cycles use handshaking between the MCU

and external peripherals to manage transfer size and data. These accesses take three

system clock cycles, again with no wait states. During regular cycles, wait states can

be inserted as needed by bus control logic. Refer to 4.5.2 Regular Bus Cycles for

more information.

NOTES:

1. The CPU32 does not support misaligned transfers.

2. Three-byte transfer cases occur only as a result of a long word to byte transfer.

Table 4-13 Operand Transfer Cases

Read Cycles Write Cycles

Nu

m

Transfer Case SIZ

[1:0]

ADDR0 DSACK

[1:0]

DATA

[15:8]

DATA

[7:0]

DATA

[15:8]

DATA

[7:0]

Next

Cycle

1 Byte to 8-Bit Port (Even/Odd) 01 X 10 OP0 — OP0 (OP0) —

2 Byte to 16-Bit Port (Even) 01 0 01 OP0 — OP0 (OP0) —

3 Byte to 16-Bit Port (Odd) 01 1 01 — OP0 (OP0) OP0 —

4 Word to 8-Bit Port (Aligned) 10 0 10 OP0 — OP0 (OP1) 1

5 Word to 8-Bit Port (Misaligned)

1

10 1 10 OP0 — OP0 (OP0) 1

6 Word to 16-Bit Port (Aligned) 10 0 11 OP0 OP1 OP0 OP1 —

7 Word to 16-Bit Port (Misaligned)

1

10 1 01 — OP0 (OP0) OP0 2

8 Long Word to 8-Bit Port (Aligned) 00 0 10 OP0 — OP0 (OP1) 13

9 Long Word to 8-Bit Port (Misaligned)

1

10 1 10 OP0 — OP0 (OP0) 12

10 Long Word to 16-Bit Port (Aligned) 00 0 01 OP0 OP1 OP0 OP1 6

11 Long Word to 16-Bit Port

(Misaligned)

1

10 1 01 — OP0 (OP0) OP0 2

12 3 Byte to 8-Bit Port (Aligned)

2

11 0 10 OP0 — OP0 (OP1) 5

13 3 Byte to 8-Bit Port (Misaligned)

2

11 1 10 OP0 — OP0 (OP0) 4

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...