ELECTRICAL CHARACTERISTICS MC68332

A-24 USER’S MANUAL

Notes for Tables A–8 and A–8a:

1. All AC timing is shown with respect to 20% V

DD

and 70% V

DD

levels unless otherwise noted.

2. When the previous bus cycle is not an ECLK cycle, the address may be valid before ECLK goes low.

3. Address access time = t

Ecyc

– t

EAD

– t

EDSR

.

4. Chip select access time = t

Ecyc

– t

ECSD

– t

EDSR

.

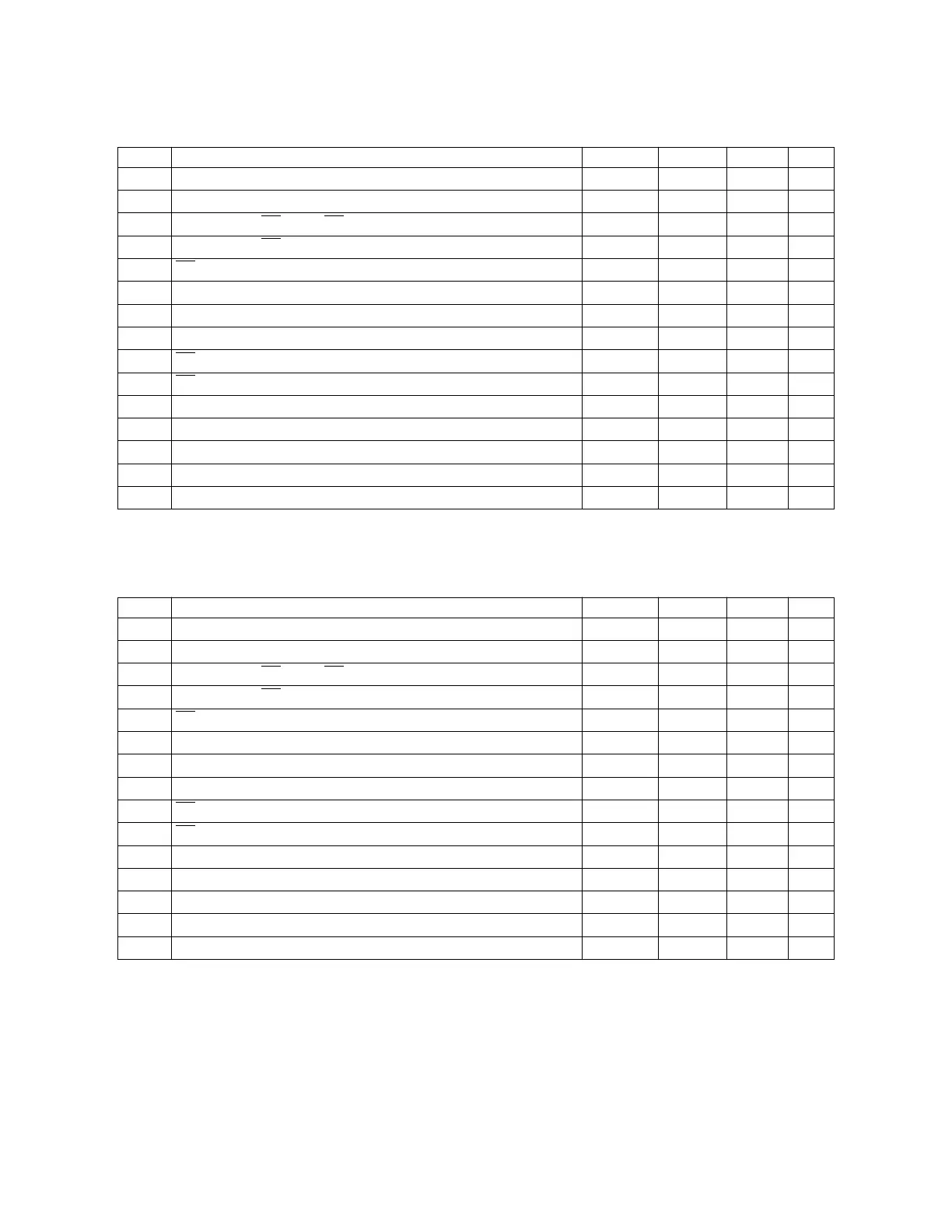

Table A-8 16.78 MHz ECLK Bus Timing

(V

DD

= 5.0 Vdc ± 10%, V

SS

= 0 Vdc, T

A

= T

L

to T

H

)

Num Characteristic Symbol Min Max Unit

E1 ECLK Low to Address Valid

2

t

EAD

—60ns

E2 ECLK Low to Address Hold t

EAH

15 — ns

E3 ECLK Low to CS

Valid (CS delay) t

ECSD

— 150 ns

E4 ECLK Low to CS

Hold t

ECSH

15 — ns

E5 CS

Negated Width t

ECSN

30 — ns

E6 Read Data Setup Time t

EDSR

30 — ns

E7 Read Data Hold Time t

EDHR

5—ns

E8 ECLK Low to Data High Impedance t

EDHZ

—60ns

E9 CS

Negated to Data Hold (Read) t

ECDH

0—ns

E10 CS

Negated to Data High Impedance t

ECDZ

—1t

cyc

E11 ECLK Low to Data Valid (Write) t

EDDW

—2t

cyc

E12 ECLK Low to Data Hold (Write) t

EDHW

15 — ns

E13 Address Access Time (Read)

3

t

EACC

386 — ns

E14 Chip Select Access Time (Read)

4

t

EACS

296 — ns

E15 Address Setup Time t

EAS

1/2 — t

cyc

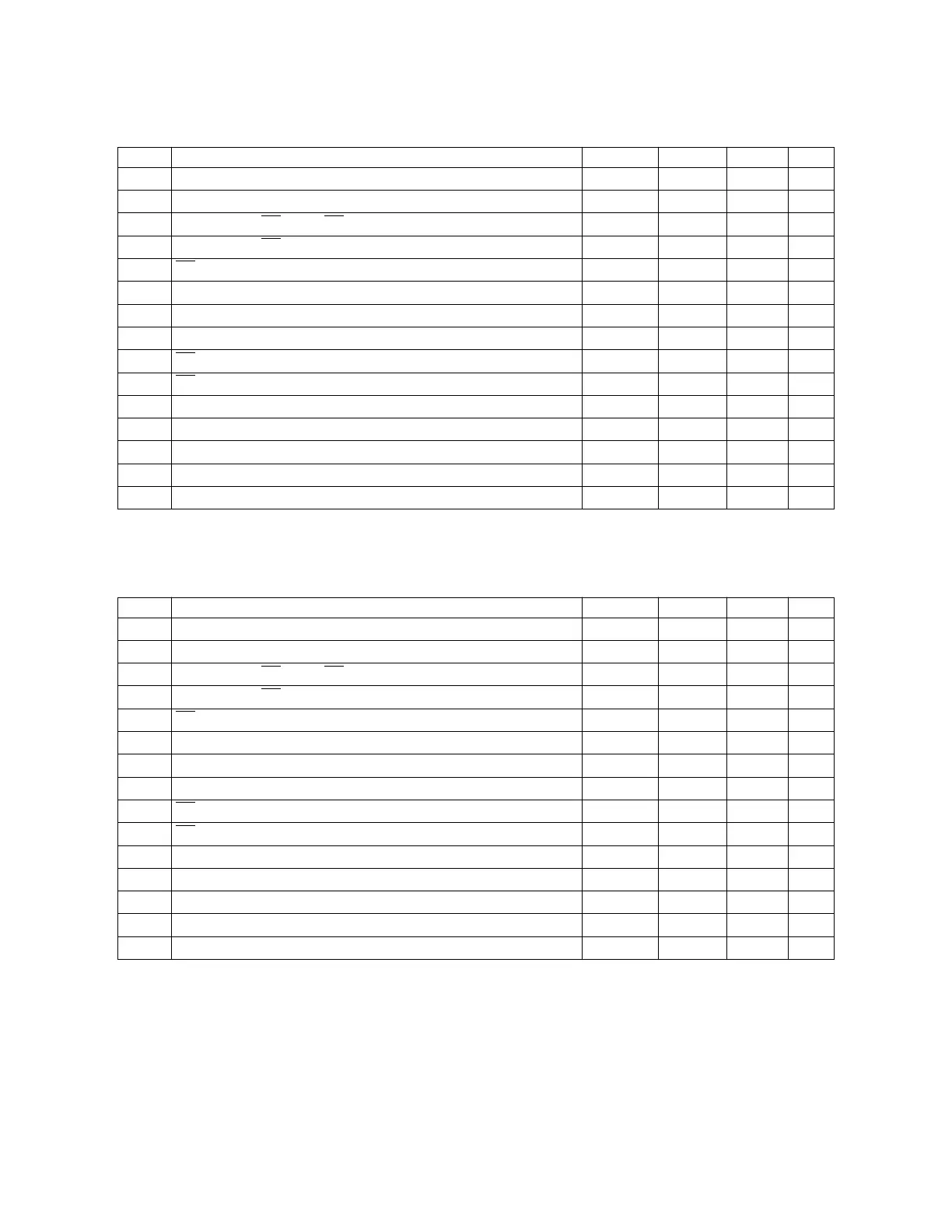

Table A-8a 20.97 MHz ECLK Bus Timing

(V

DD

= 5.0 Vdc ± 5%, V

SS

= 0 Vdc, T

A

= T

L

to T

H

)

Num Characteristic Symbol Min Max Unit

E1 ECLK Low to Address Valid

2

t

EAD

—48ns

E2 ECLK Low to Address Hold t

EAH

10 — ns

E3 ECLK Low to CS

Valid (CS delay) t

ECSD

— 120 ns

E4 ECLK Low to CS

Hold t

ECSH

10 — ns

E5 CS

Negated Width t

ECSN

25 — ns

E6 Read Data Setup Time t

EDSR

25 — ns

E7 Read Data Hold Time t

EDHR

5—ns

E8 ECLK Low to Data High Impedance t

EDHZ

—48ns

E9 CS

Negated to Data Hold (Read) t

ECDH

0—ns

E10 CS

Negated to Data High Impedance t

ECDZ

—1t

cyc

E11 ECLK Low to Data Valid (Write) t

EDDW

—2t

cyc

E12 ECLK Low to Data Hold (Write) t

EDHW

10 — ns

E13 Address Access Time (Read)

3

t

EACC

308 — ns

E14 Chip Select Access Time (Read)

4

t

EACS

236 — ns

E15 Address Setup Time t

EAS

1/2 — t

cyc

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...