8.4 Communication Methods

116

Standard Event Status Enable Register (SESER)

Setting any bit of the Standard Event Status Enable Register to 1 enables

access to the corresponding bit of the Standard Event Status Register.

Standard Event Status Register (SESR) and Standard Event Status Enable

Register (SESER)

Device-Specific Event Status Registers (ESR0 and ESR1)

This instrument provides two event status registers for controlling events.

Each event register is an 8-bit register.

When any bit in one of these event status registers enabled by its corresponding

event status enable register is set to 1, the following happens:

• For Event Status Register 0, bit 0 (ESB0) of the Status Byte Register is set to

1.

• For Event Status Register 1, bit 1 (ESB1) of the Status Byte Register is set to

1.

Event Status Registers 0 and 1 are cleared in the following situations:

• When a

*CLS command is executed

• When an Event Status Register query

(

:ESR0? or :ESR1?) is executed

• When the instrument is powered on

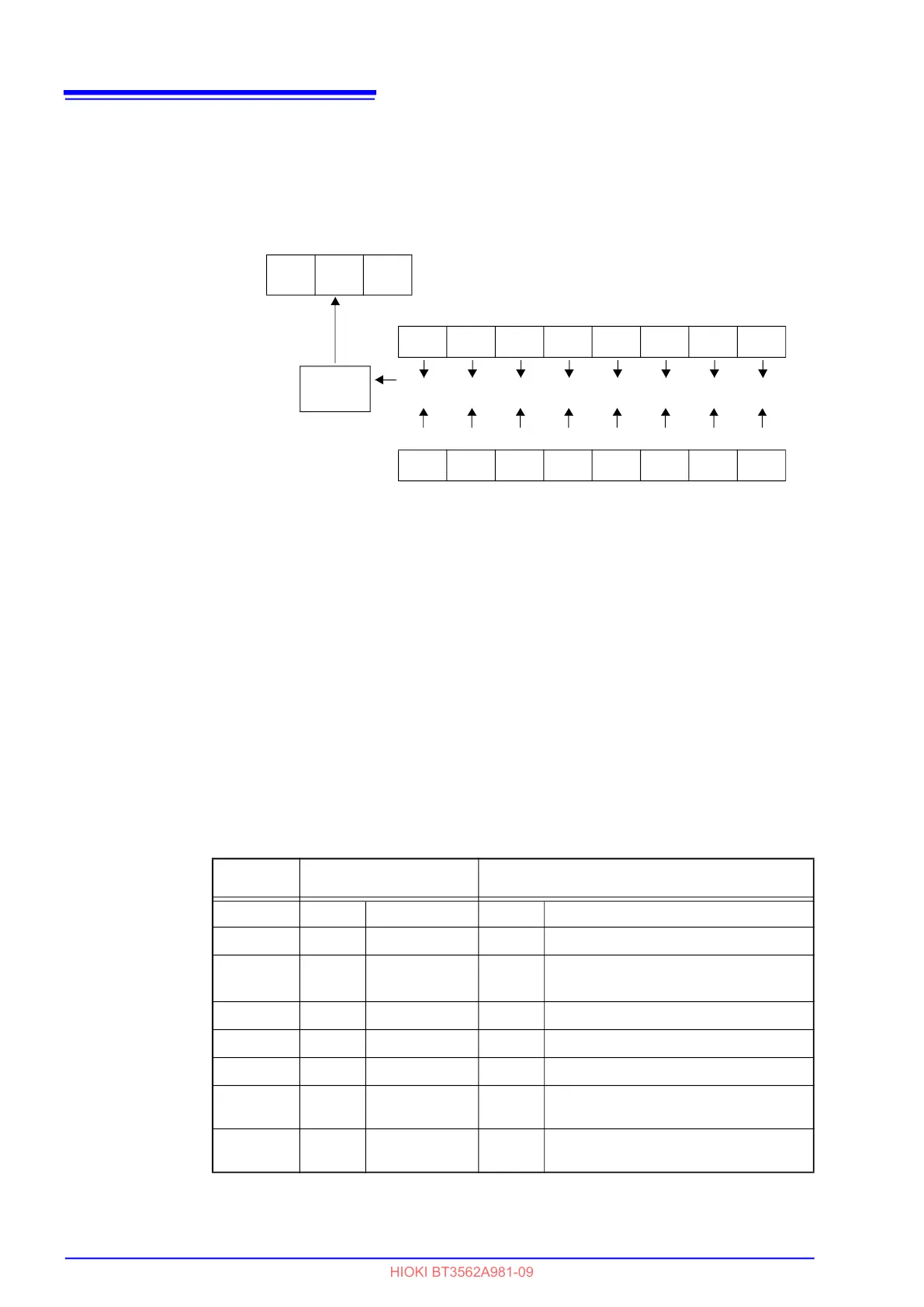

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

PON URQ CME EXE DDE QYE RQC OPC

& & & & & & & &

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

PON URQ CME EXE DDE QYE RQC OPC

Logical

OR

Standard Event Status Register (SESR)

Standard Event Status Enable Register (SESER)

bit6 bit5 bit4

SRQ

MSS

ESB MAV

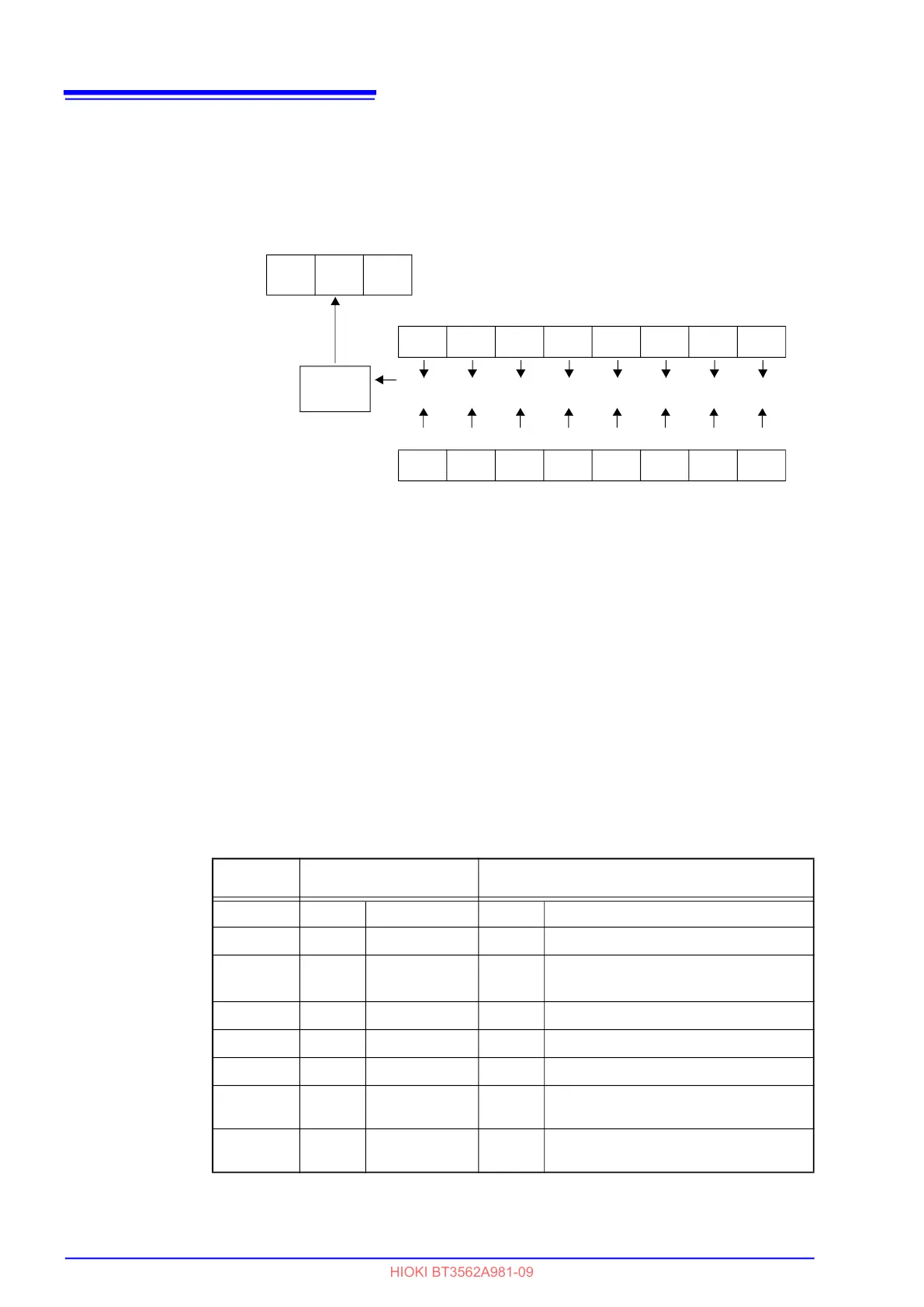

Event Status Register 0

(ESR0)

Event Status Register 1 (ESR1)

Bit 7

-- Unused -- unused

Bit 6

-- Unused

AND AND

Bit 5

ERR

Measurement

Faults

V-Hi Voltage High Comparator Result

Bit 4

--

Unused V-IN Voltage IN Comparator Result

Bit 3

--

Unused V-Lo Voltage Low Comparator Result

Bit 2

--

Unused R-Hi Resistance High Comparator Result

Bit 1

INDEX

End of Mea-

surement

R-IN Resistance IN Comparator Result

Bit 0

EOM

End of Conver-

sion

R-Lo Resistance Low Comparator Result

Loading...

Loading...