A

PPENDIX

A-2 FC6A S

ERIES

MICROS

MART

L

ADDER

P

ROGRAMMING

M

ANUAL

FC9Y-B1726

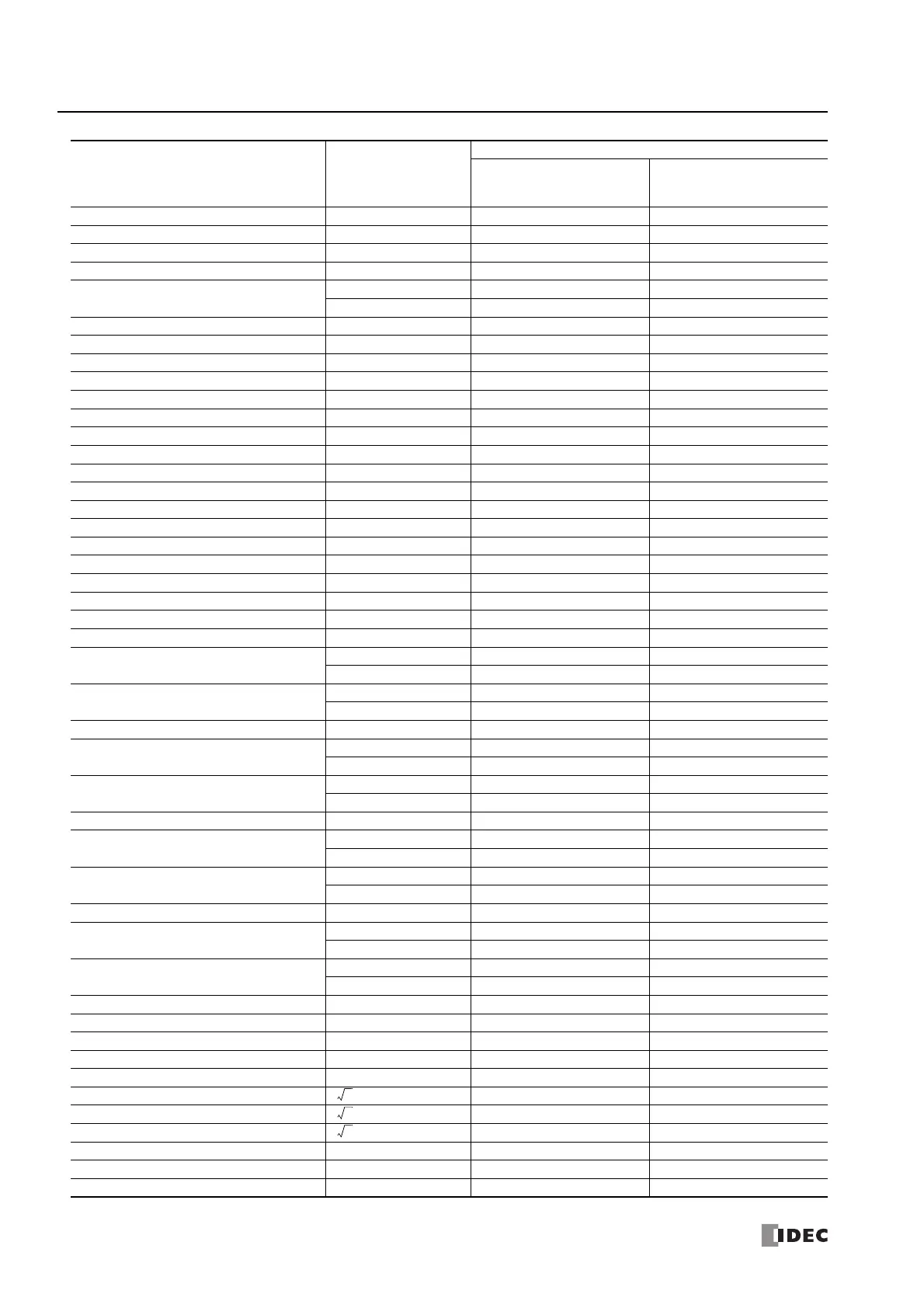

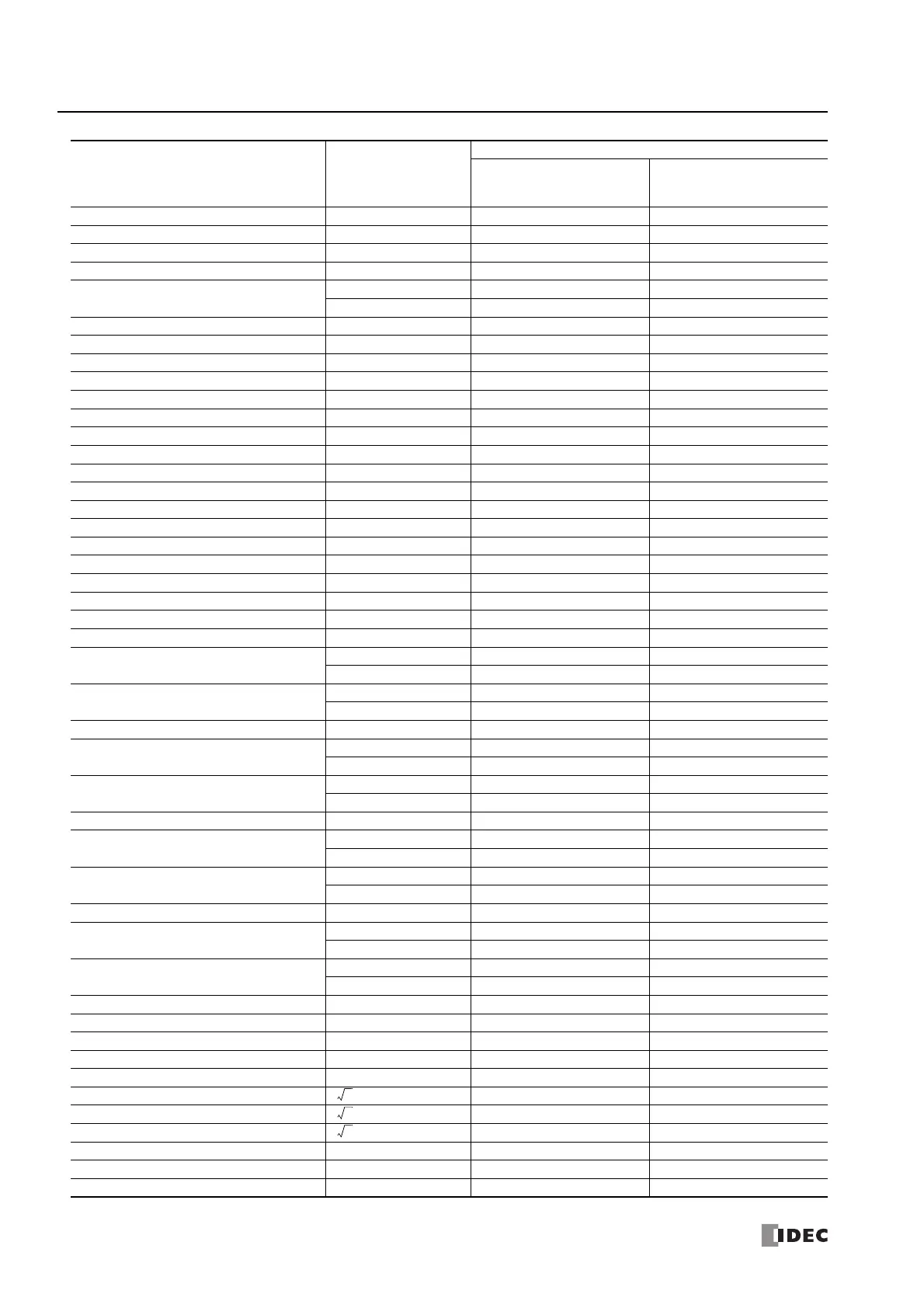

IMOV, IMOVN (D) D+D→D+D 18.8 9.4

IMOV (F) ― 13.9 7.00

MOVC ―― ―

BMOV D→D 16.1 + 1.2n 8.1 + 0.6n

IBMV, IBMVN

M+D→M+D 13.4 6.7

D+D→D+D 13.4 6.7

NSET (W, I) D→D 2.28 + 2.2n 1.14 +1.1n

NSET (D, L) D→D 2.2 + 12.6n 1.1 + 6.3n

NSET (F) D→D 2.2 + 12.6n 1.1 + 6.3n

NRS (W, I) D, D→D 5.84 + 0.64n 2.92 + 0.32n

NRS (D, L) D, D→D 11.1 + 5.7n 5.6 + 2.9n

NRS (F) D, D→D 11.0 + 5.8n 5.5 + 2.9n

XCHG (W) D⇔D 5.32 2.66

XCHG (D) D⇔D 26.0 13.0

TCCST (W) D→T 4.68 2.34

TCCST (D) D→T 15.0 7.5

CMP (=, <>, <, >, <=, >=) (W, I) D⇔D→M 27.6 13.8

CMP (=, <>, <, >, <=, >=) (D, L) D⇔D→M 38.0 19.0

CMP (=, <>, <, >, <=, >=) (F) D⇔D→M 38.2 19.1

ICMP (>=) D⇔D⇔D→M 29.0 14.5

ICMP (D, L, F) D⇔D⇔D→M 44.6 22.3

LC (=, <>,<, >, <=, >=) (W, I) D⇔D 4.84 2.42

LC (=, <>,<, >, <=, >=) (D, L) D⇔D 15.2 7.6

LC (=, <>,<, >, <=, >=) (F) D⇔D 15.3 7.7

ADD (W, I)

M+M→D 11.6 5.8

D+D→D 11.7 5.9

ADD (D, L)

M+M→D 27.2 13.6

D+D→D 27.2 13.6

ADD (F) D+D→D 27.8 13.9

SUB (W, I)

M-M→D 11.6 5.8

D-D→D 11.7 5.9

SUB (D, L)

M-M→D 27.2 13.6

D-D→D 27.2 13.6

SUB (F) D-D→D 27.4 13.7

MUL (W, I)

M×M→D 11.2 5.6

D×D→D 11.3 5.7

MUL (D, L)

M×M→D 27.2 13.6

D×D→D 27.2 13.6

MUL (F) D×D→D 27.4 13.7

DIV (W, I)

M÷M→D7.03.5

D÷D→D 6.96 3.48

DIV (D, L)

M÷M→D 28.0 14.0

D÷D→D 28.0 14.0

DIV (F) D÷D→D 28.0 14.0

INC (W, I) ― 8.92 4.46

INC (D, L) ― 19.3 9.65

DEC (W, I) ― 8.92 4.46

DEC (D, L) ― 19.2 9.6

ROOT (W) 6.24 3.12

ROOT (D) 18.0 9.0

ROOT (F) 19.4 9.7

SUM (W, I) D, D→D 11.3 + 0.8n 5.7 + 0.4n

SUM (D, L) D, D→D 16.6 + 6.0n 8.3 + 3.0n

SUM (F) D, D→D 16.8 + 7.0n 8.4 + 3.5n

Instruction Device and Condition

Execution Time (μs)

All-in-One CPU Module/

CAN J1939 All-in-One CPU

Module

Plus CPU Module

Loading...

Loading...