The Intel Quartus Prime software generates a .sof/.rbf file containing the FPGA design information. You can use

the .sof/.rbf file with a JTAG programmer to configure the Intel Agilex device. The Intel FPGA Download Cable II and the

Intel FPGA Ethernet Cable both can support the V

CCIO_SDM

supply at 1.8 V. Alternatively, you can use the Jam STAPL Format

File (.jam) or Jam Byte Code File (.jbc) for JTAG configuration. After the JTAG configuration, the host executes

CONFIG_STATUS SDM command to ensure the configuration is successful.

Intel Agilex devices automatically compress the configuration bitstream. You cannot disable compression in Intel Agilex

devices.

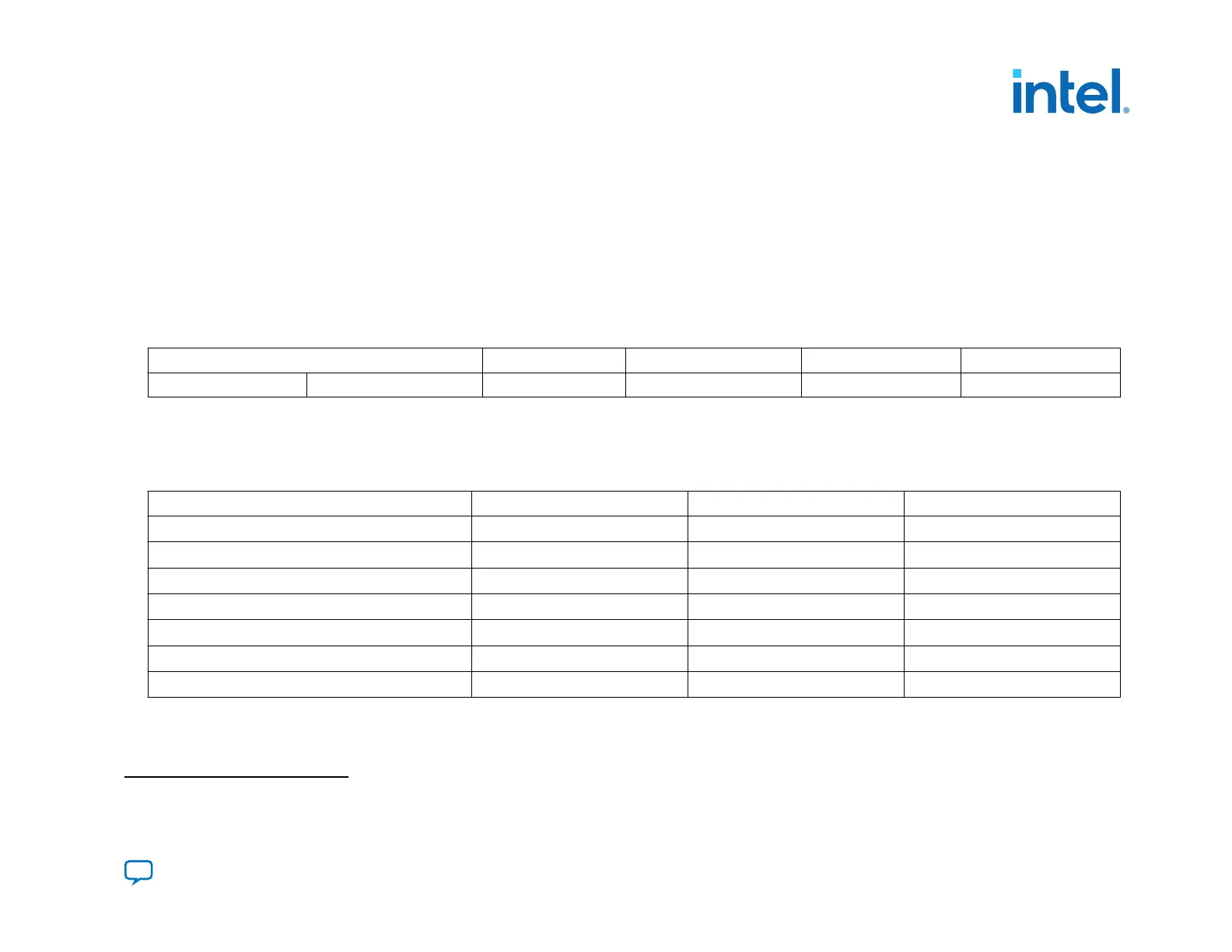

Table 37. Intel Agilex Configuration Data Width, Clock Rates, and Data Rates

Mbps is an abbreviation for Megabits per second.

Mode Data Width (bits) Max Clock Rate Max Data Rate MSEL[2:0]

Passive JTAG 1 30 MHz 30 Mbps 3'b111

Note:

The JTAG port has the highest priority and overrides the MSEL pin settings. Consequently, you can configure the Intel Agilex

device over JTAG even if the MSEL pin specify a different configuration scheme unless you disabled JTAG for security reasons.

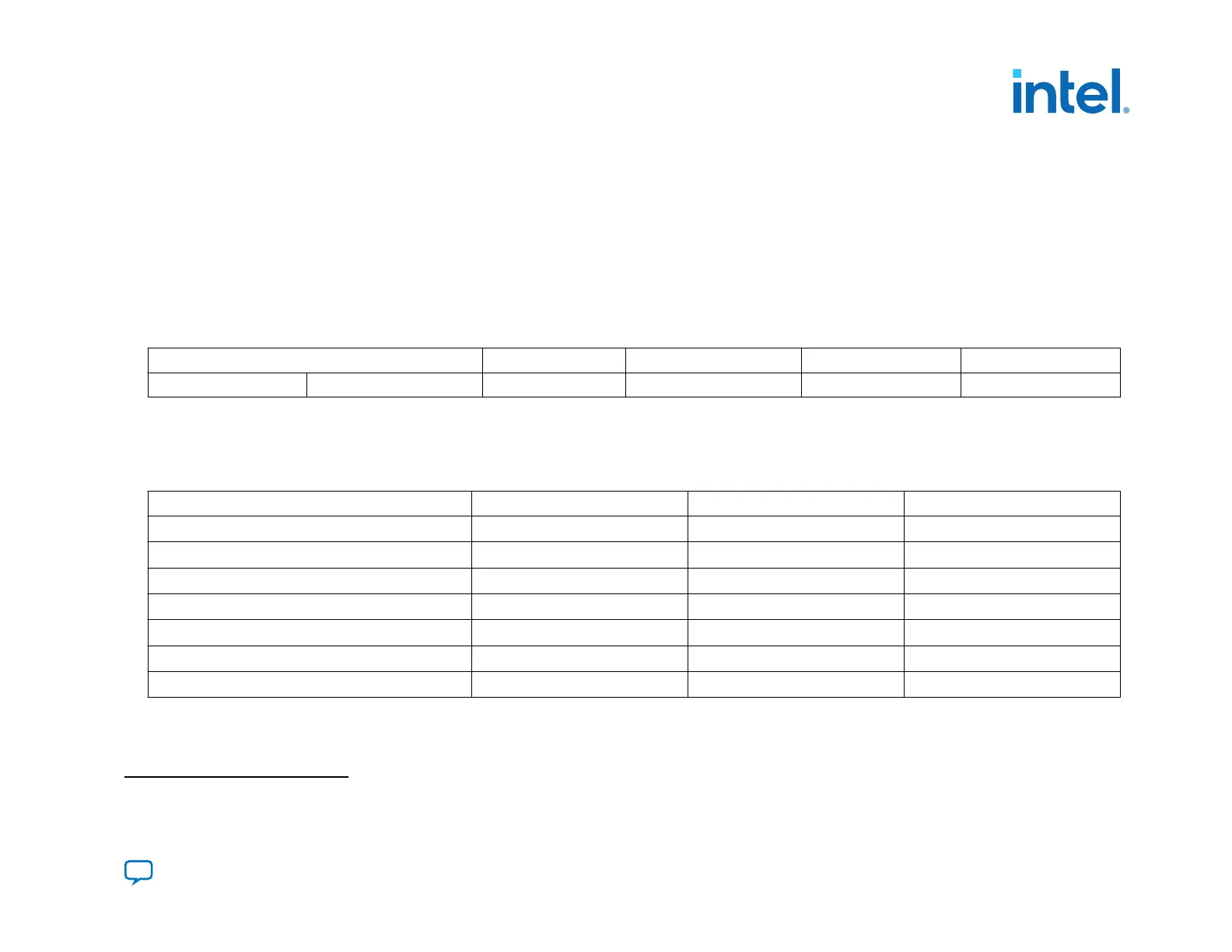

Table 38. Power Rails for the Intel Agilex Device Configuration Pins

Configuration Function Pin Type Direction Powered by

TCK

Fixed Input V

CCIO_SDM

TDI

(13)

Fixed Input V

CCIO_SDM

TMS

(13)

Fixed Input V

CCIO_SDM

TDO

(13)

Fixed Output V

CCIO_SDM

nSTATUS

SDM I/O Output V

CCIO_SDM

nCONFIG

SDM I/O Input V

CCIO_SDM

MSEL[2:0]

SDM I/O Input V

CCIO_SDM

Note: Pin-Out files are not yet available for Intel Agilex devices.

(13)

The JTAG pins can access the HPS JTAG chain in Intel Agilex SoC devices.

3. Intel Agilex Configuration Schemes

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

125

Loading...

Loading...