During configuration global configuration control signals hold the core fabric in a frozen state to prevent electrical contention.

The LSMs work in parallel to asynchronously unfreeze the sectors. Within a sector the LSM unfreezes LAB rows and registers

in the LABs sequentially. The LSMs work to unfreeze the fabric in parallel across all sectors without synchronization.

Consequently, logic in different sectors or in the same sector but in different rows could begin to operate while other logic is

still frozen. The INIT_DONE signal asserts when all the LSMs have entered user mode.

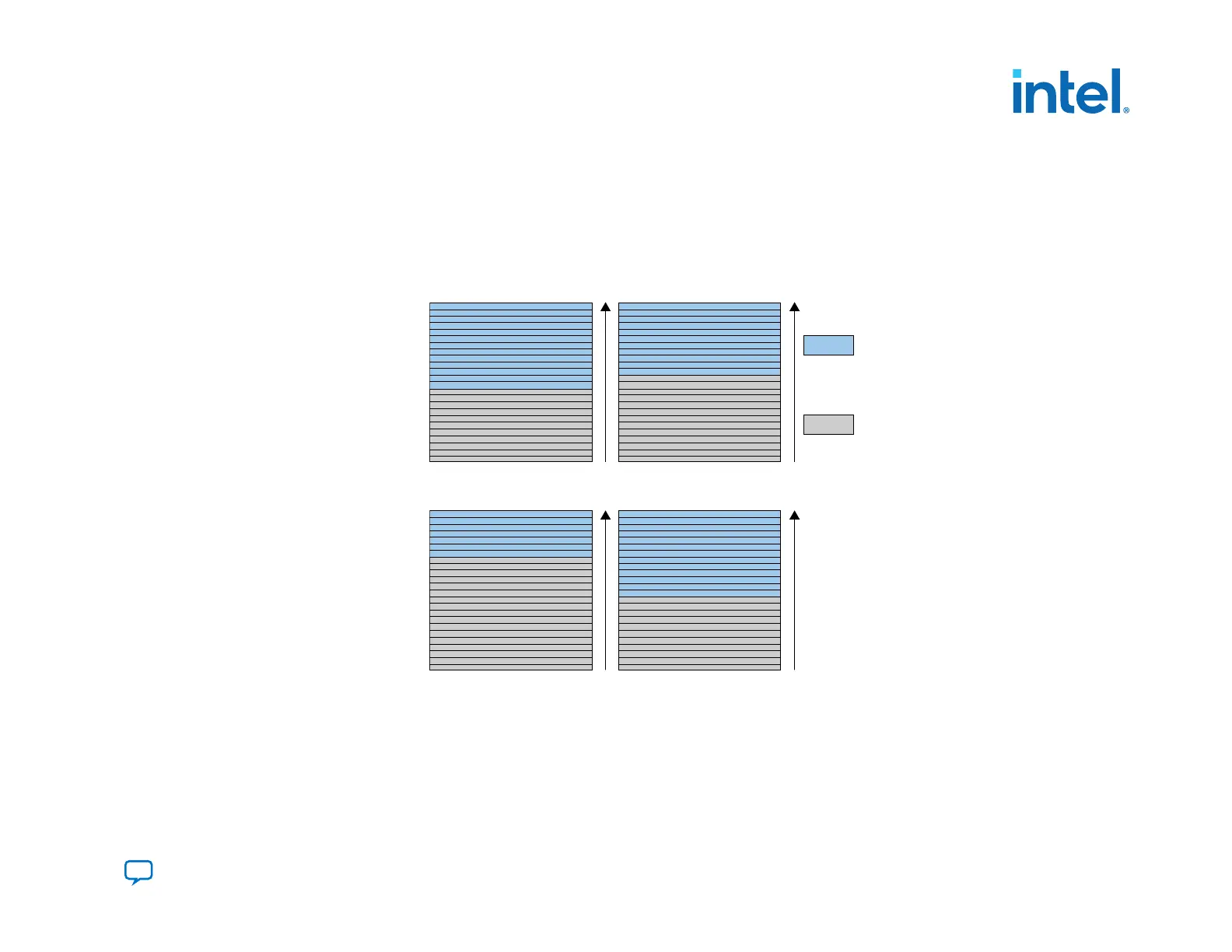

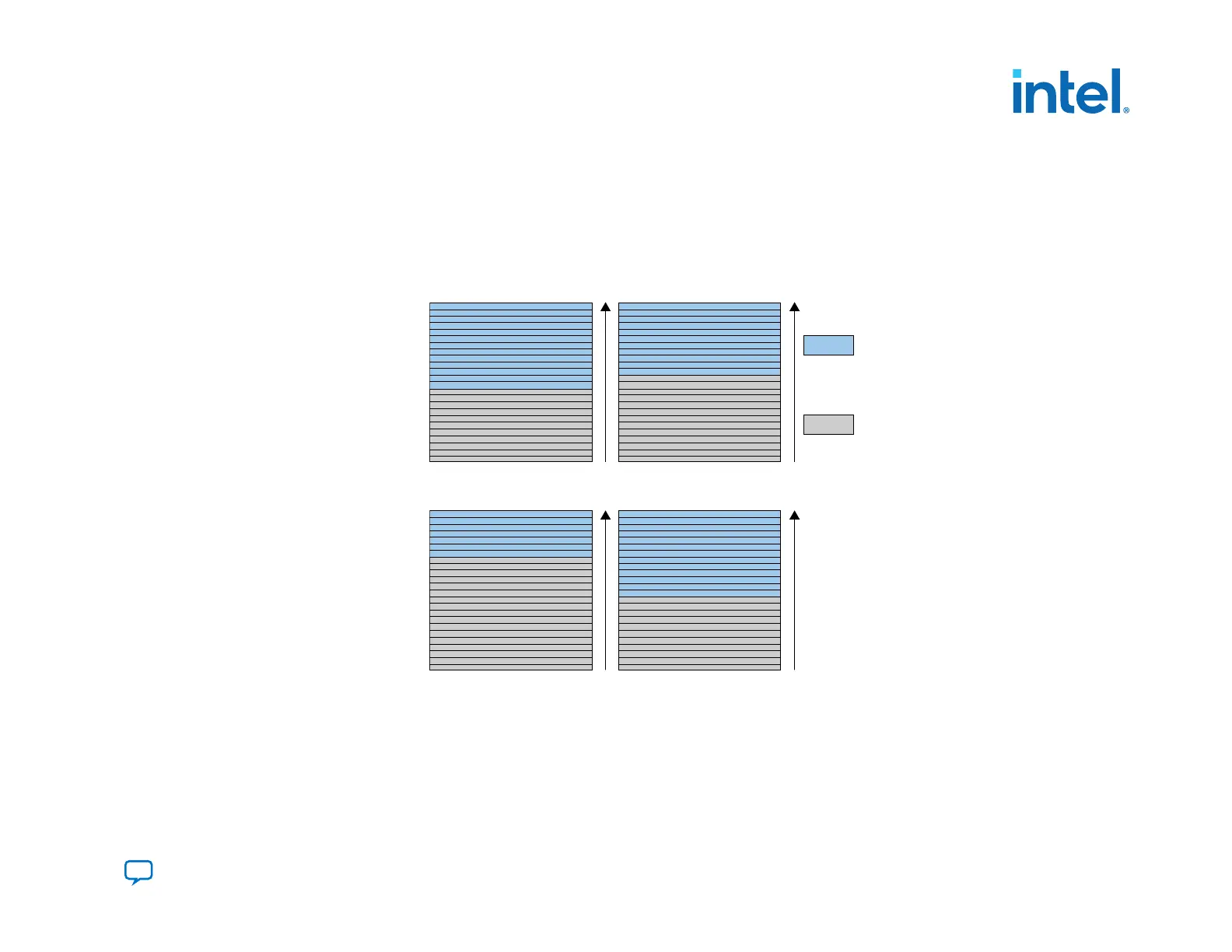

Figure 57. Releasing LAB Rows and Registers in the LABs Sequentially and Asynchronously Across Sectors

Release From Reset

Sector Sector

Sector Sector

Frozen

Functional

The following topics provide more detail about device configuration and initialization, and possible consequences if you do not

use the Reset Release IP to hold the Intel Agilex device in reset until entire fabric enters user mode.

4. Including the Reset Release Intel FPGA IP in Your Design

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

139

Loading...

Loading...