Model 2750 Multimeter/Switch System User’s Manual Status Structure 11-11

Status register sets

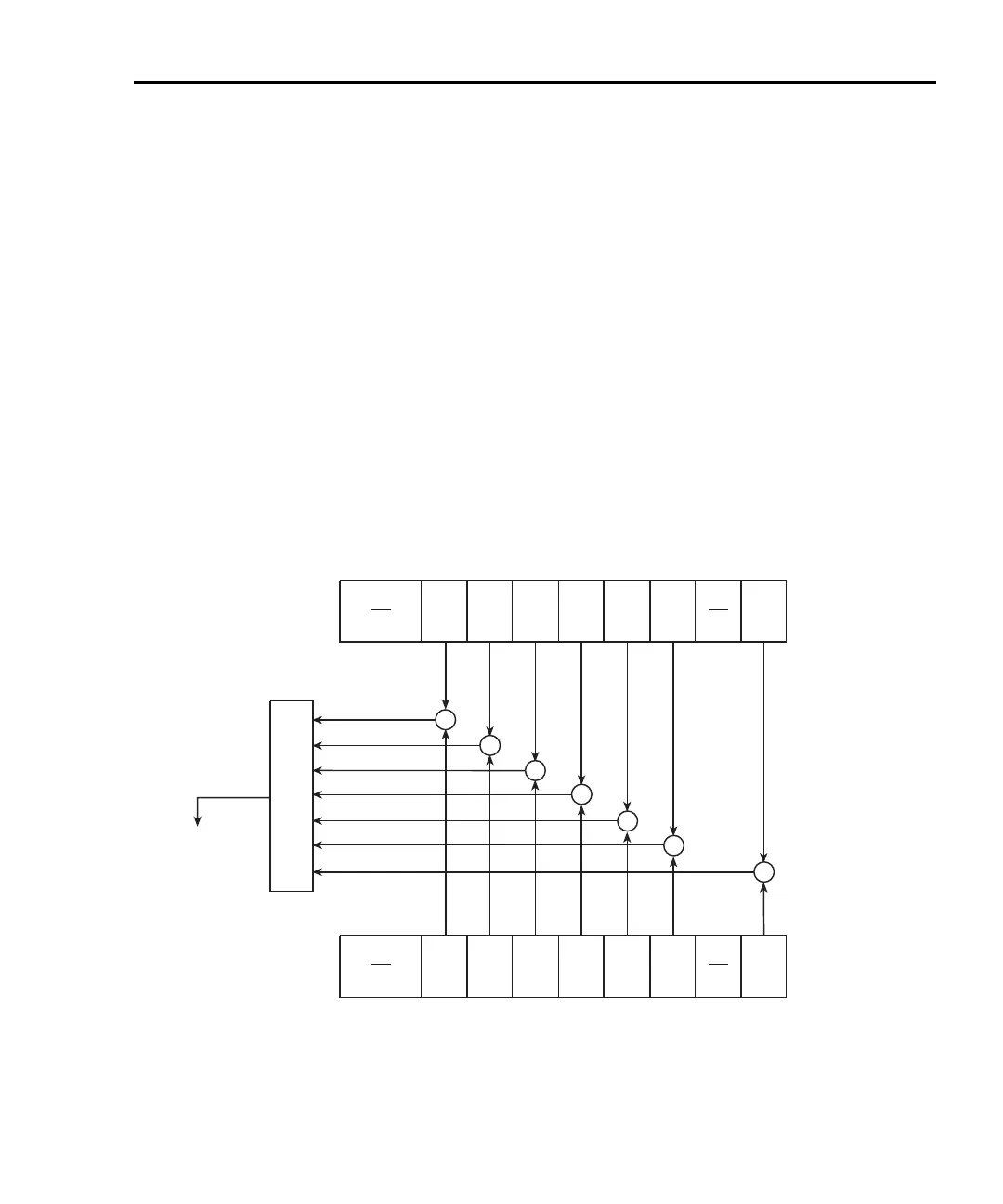

As shown in Figure 11-1, there are four status register sets in the status structure of the

Model 2750: Standard Event Status, Operation Event Status, Measurement Event Status,

and Questionable Event Status.

Register bit descriptions

Standard event register

The used bits of the Standard Event Register (Figure 11-4) are described as follows:

• Bit B0, Operation Complete (OPC) — Set bit indicates that all pending selected

device operations are completed and the Model 2750 is ready to accept new com-

mands. This bit only sets in response to the *OPC? query command. See

Section 12 for details on *OPC and *OPC?.

Figure 11-4

Standard event status

* ESR ?

PON

(B7)

URQ

(B6)

CME

(B5)

EXE

(B4)

DDE

(B3)

QYE

(B2) (B1) (B0)

OR

Standard Event

Status Register

Standard Event

Status Enable

Register

PON = Power On

URQ = User Request

CME = Command Error

EXE = Execution Error

DDE = Device-Dependent Error

OPC

PON

(B7)

URQ

(B6)

CME

(B5)

EXE

(B4)

DDE

(B3)

QYE

(B2) (B1) (B0)

OPC

* ESE

* ESE ?

(B15 - B8)

(B15 - B8)

To Event

Summary

Bit (ESB) of

Status Byte

Register.

&

&

&

&

&

&

&

QYE = Query Error

OPC = Operation Complete

& = Logical AND

OR = Logical OR

2750-900-01.book Page 11 Wednesday, August 3, 2011 7:56 AM

Loading...

Loading...