Pin and Signal Descriptions

Pin Descriptions

Copyright © 2008 Marvell Doc. No. MV-S104859-U0 Rev. E

December 2, 2008, Preliminary Document Classification: Proprietary Information Page 25

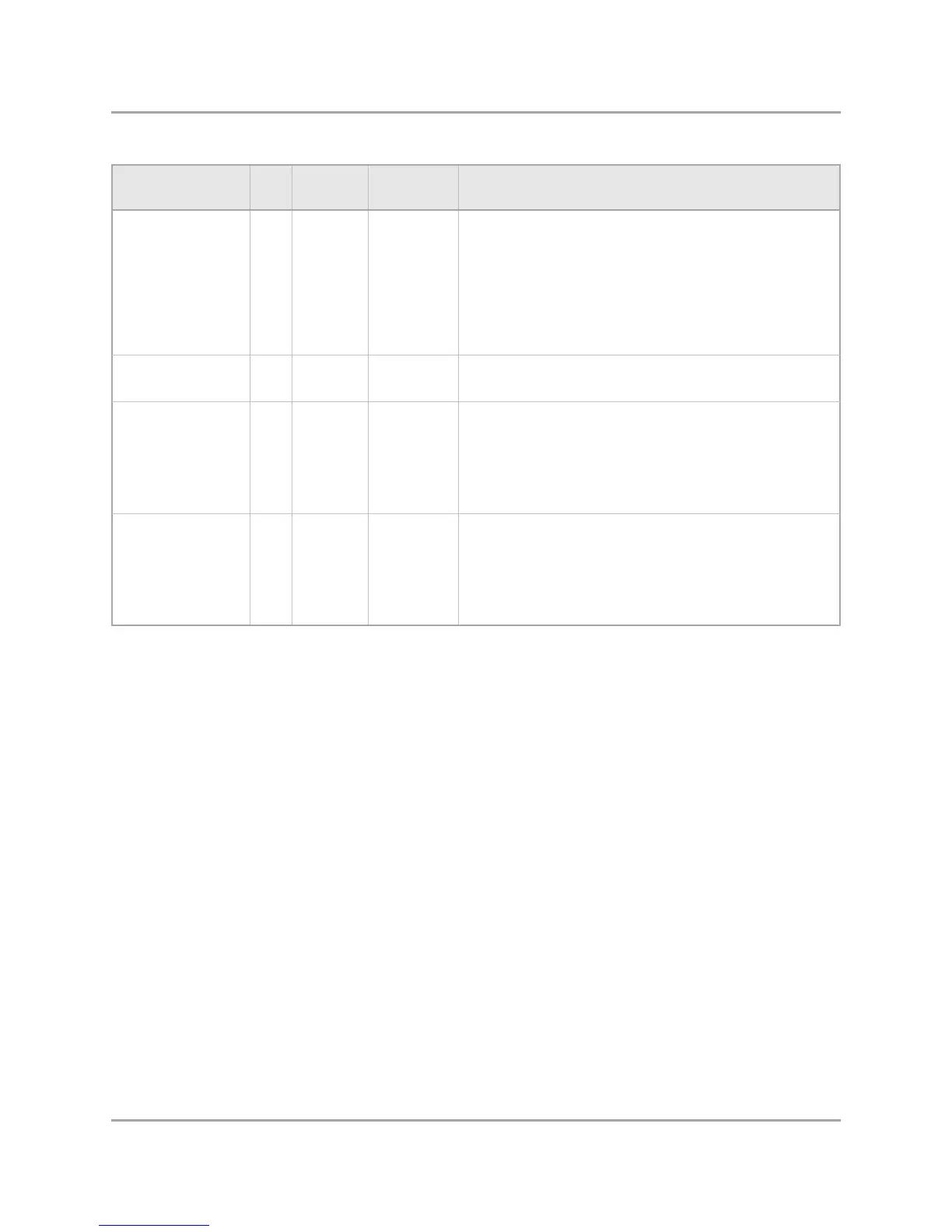

M_STARTBURST O SSTL VDD_M Start Burst

88F6281 indication of starting a burst read transaction.

Asserted with the first M_CASn cycle of SDRAM access.

NOTE: Must be routed on board to the SDRAM, and back to

the 88F6281 as M_STARTBURST_IN. For the

recommended length calculation for this routing and

termination requirements, see the 88F6180, 88F6190,

88F6192, and 88F6281 Design Guide.

M_START

BURST_IN

I SSTL VDD_M Start Burst Input

M_PCAL I Calib SDRAM interface P channel output driver calibration. Connect

to VSS through a resistor. The resistor value can vary

between 30–70 ohm.

NOTE: See the 88F6180, 88F6190, 88F6192, and 88F6281

Design Guide for the recommended values of the

calibration resistors.

M_NCAL I Calib SDRAM interface N channel output driver calibration. Connect

to M_VDD through a resistor. The resistor value can vary

between 30–70 ohm.

NOTE: See the 88F6180, 88F6190, 88F6192, and 88F6281

Design Guide for the recommended values of the

calibration resistors.

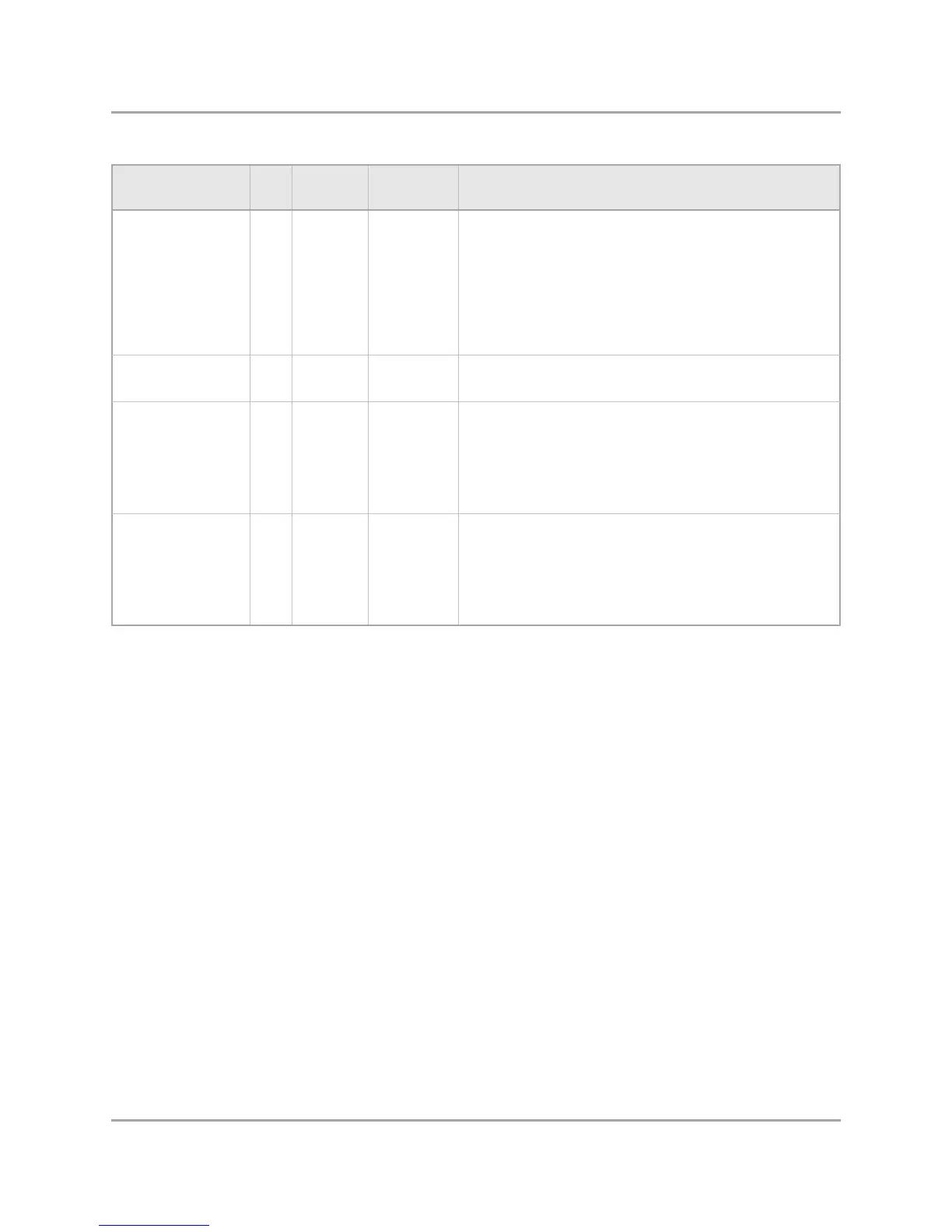

Table 5: DDR SDRAM Interface Pin Assignments (Continued)

Pin Name I/O Pin

Type

Power

Rail

Description

Loading...

Loading...