Pin and Signal Descriptions

Pin Descriptions

Copyright © 2008 Marvell Doc. No. MV-S104859-U0 Rev. E

December 2, 2008, Preliminary Document Classification: Proprietary Information Page 31

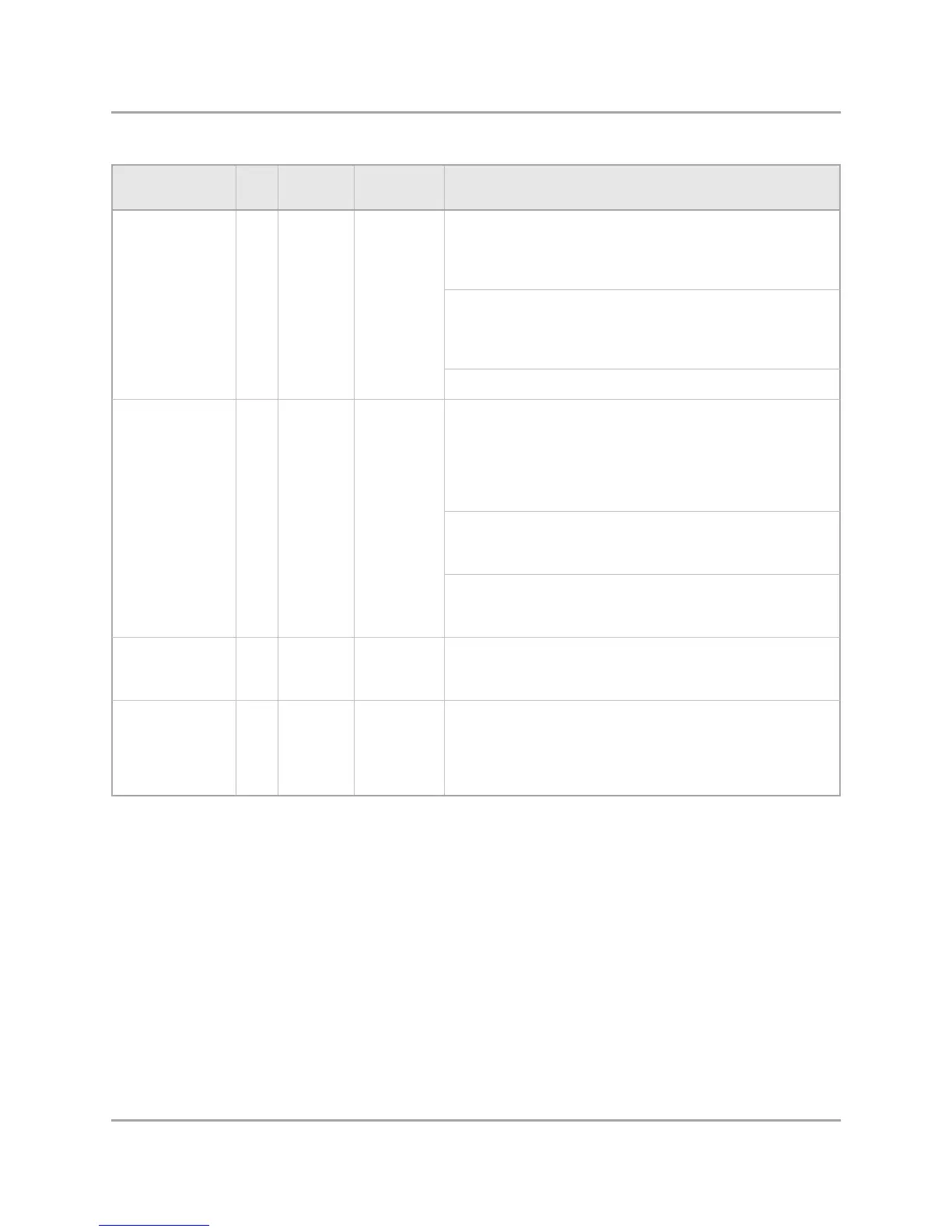

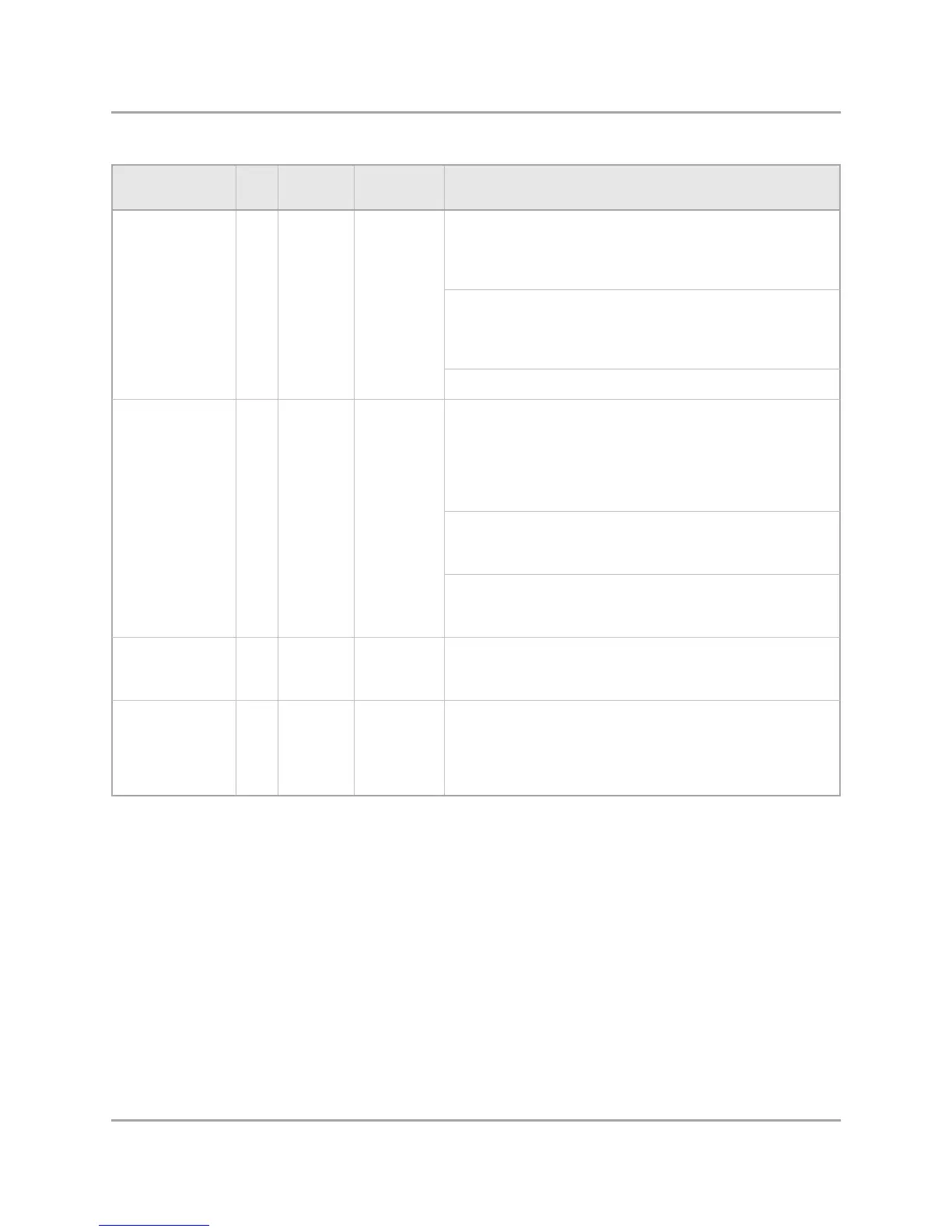

MPP[32]/GE1[12] I/O CMOS VDD_GE_B RGMII Transmit Clock

RGMII transmit reference output clock for GE_TXD[3:0] and

GE_TXCTL Provides 125 MHz, 25 MHz or 2.5 MHz clock.

Not used in MII/MMII mode.

MII/MMII Carrier Sense

Indicates that the receive medium is non-idle. In half-duplex

mode, GE_CRS is also asserted during transmission. Carrier

sense is not synchronous to any clock.

GMII Carrier Sense

MPP[33]/GE1[13] t/s

O

CMOS VDD_GE_B RGMII Transmit Control

Transmit control synchronous to the GE_TXCLKOUT output

rising/falling edge.

GE_TXEN is presented on the rising edge of GE_TXCLKOUT.

A logical derivative of transmit enable transmit error is presented

on the falling edge of GE_TXCLKOUT.

MII/MMII Transmit Error

It is synchronous to transmit clock.

NOTE: Multiplexed on MPP.

GMII Transmit Error

It Is synchronous to GE_TXCLKOUT.

NOTE: Multiplexed on MPP.

MPP[34]/GE1[14] O CMOS VDD_GE_B MII/MMII Transmit Enable

Indicates that the packet is being transmitted to the PHY. It Is

synchronous to transmit clock.

MPP[35]/GE1[15] I CMOS VDD_GE_B MII/MMII Receive Error

Indicates that an error symbol, a false carrier, or a carrier

extension symbol is detected on the cable. It is synchronous to

GE_RXCLK input.

NOTE: Multiplexed on MPP.

Table 8: Gigabit Ethernet Port0/1 Interface Pin Assignments (Continued)

Pin Name I/O Pin

Type

Power

Rail

Description

Loading...

Loading...