MS51

Nov. 28, 2019 Page 209 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

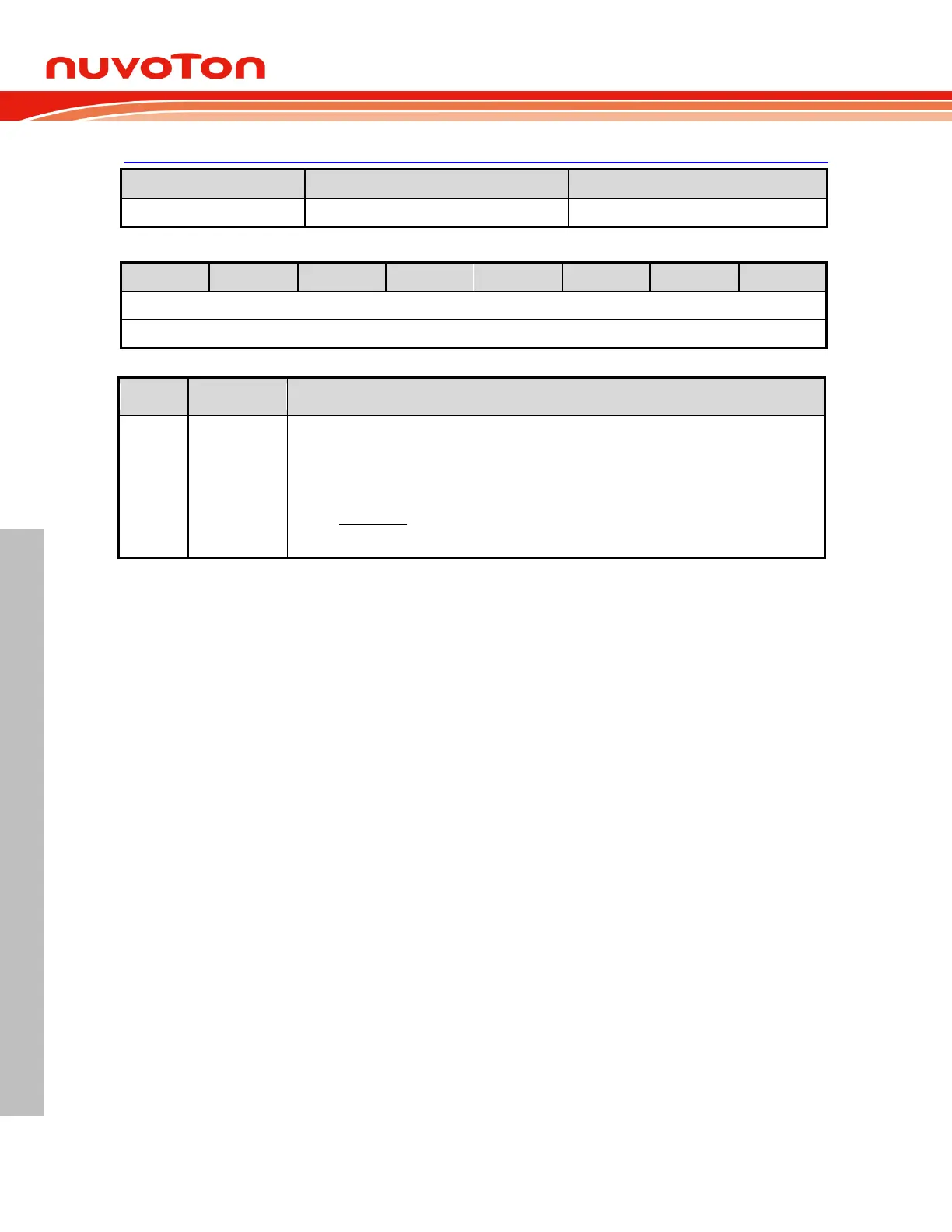

CKDIV – Clock Divider

Clock divider

The system clock frequency FSYS follows the equation below according to CKDIV value.

, while CKDIV = 01H to FFH.

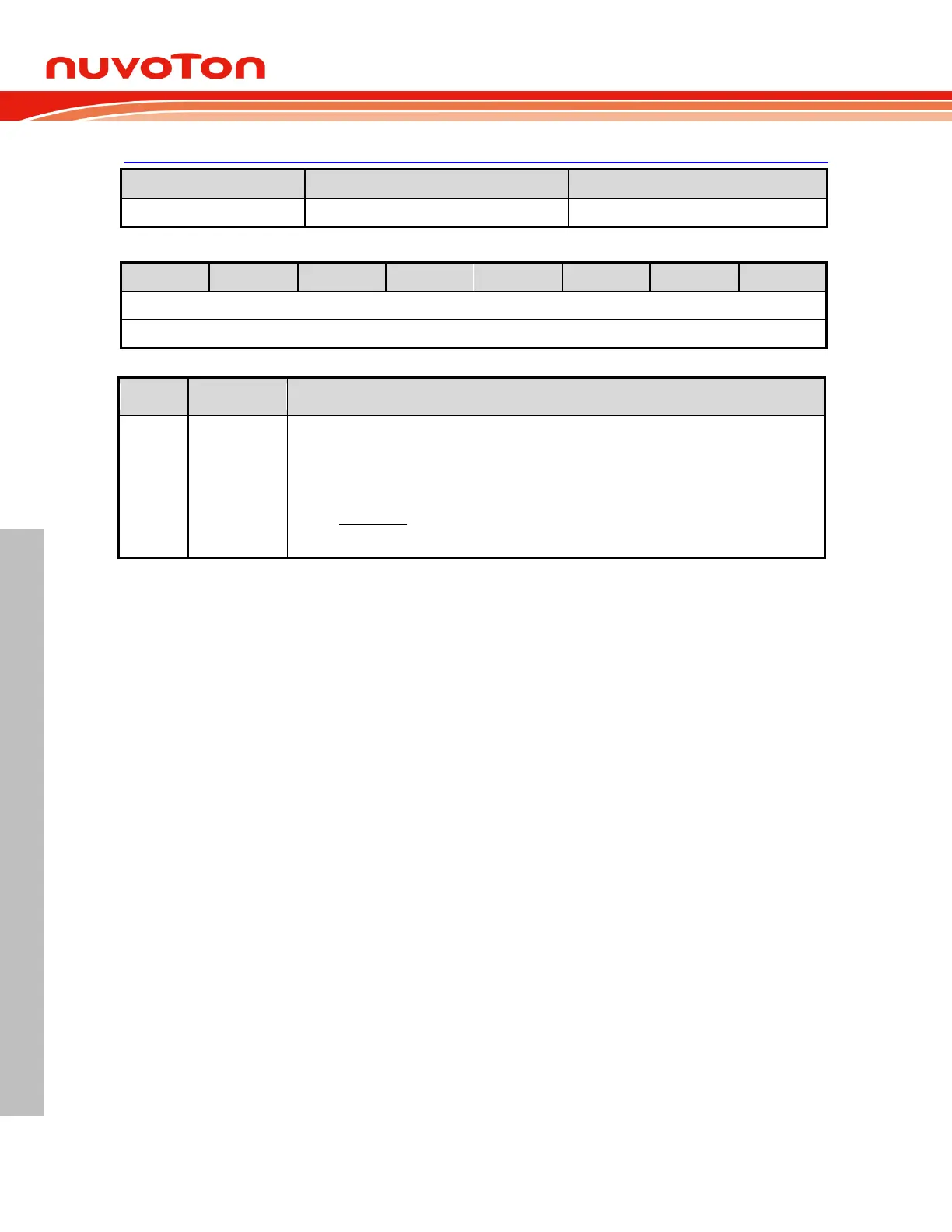

System Clock Output 6.2.1.7

The MS51 provides a CLO pin that outputs the system clock. Its frequency is the same as F

SYS

. The

output enable bit is CLOEN (CKCON.1). CLO output stops when device is put in its Power-down mode

because the system clock is turned off. Note that when noise problem or power consumption is

important issue, user had better not enable CLO output.

Loading...

Loading...