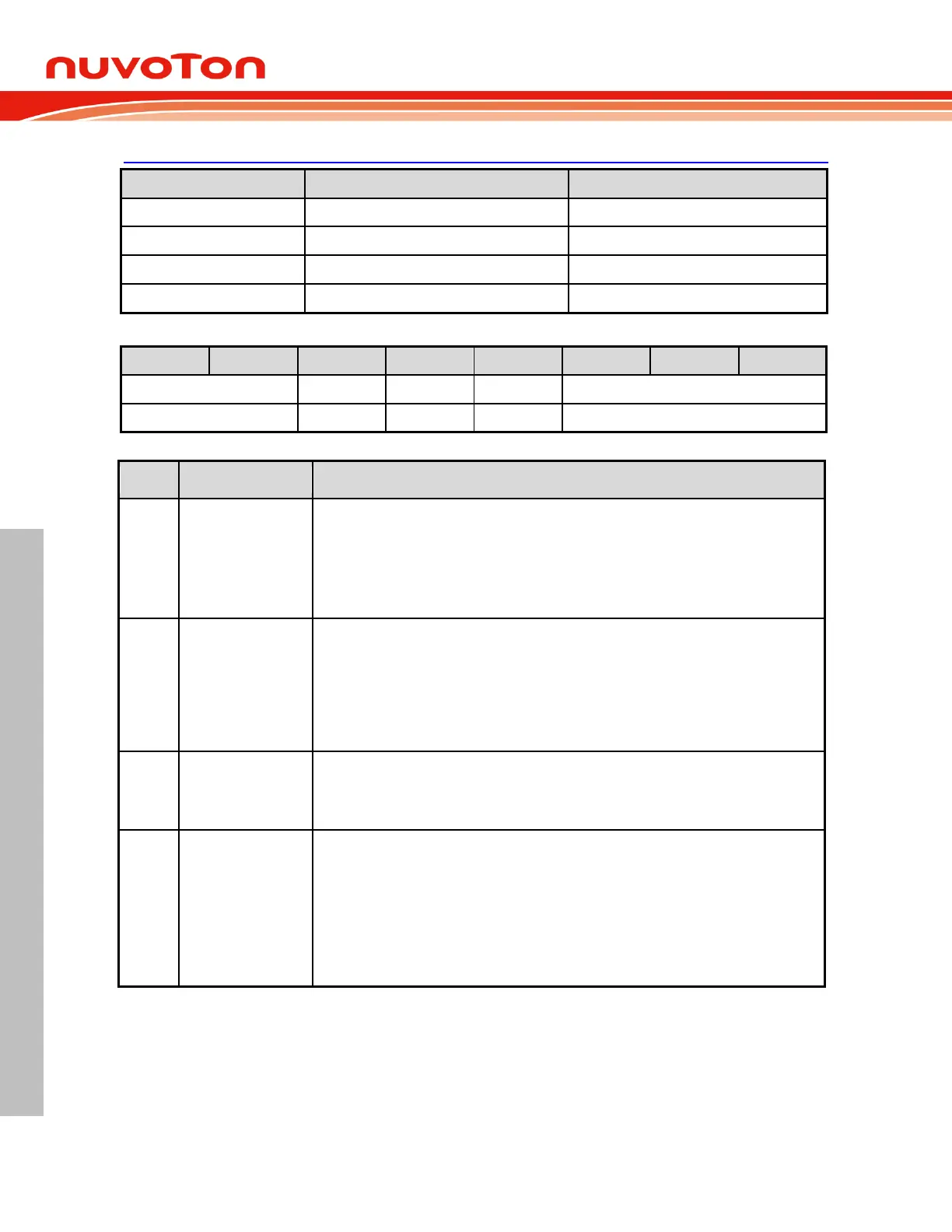

Group mode enable

This bit enables the group mode. If enabled, the duty of first three pairs of PWM are decided

by PWM01H and PWM01L rather than their original duty control registers.

0 = Group mode Disabled.

1 = Group mode Enabled.

Note: This bit is only valid in PWM0

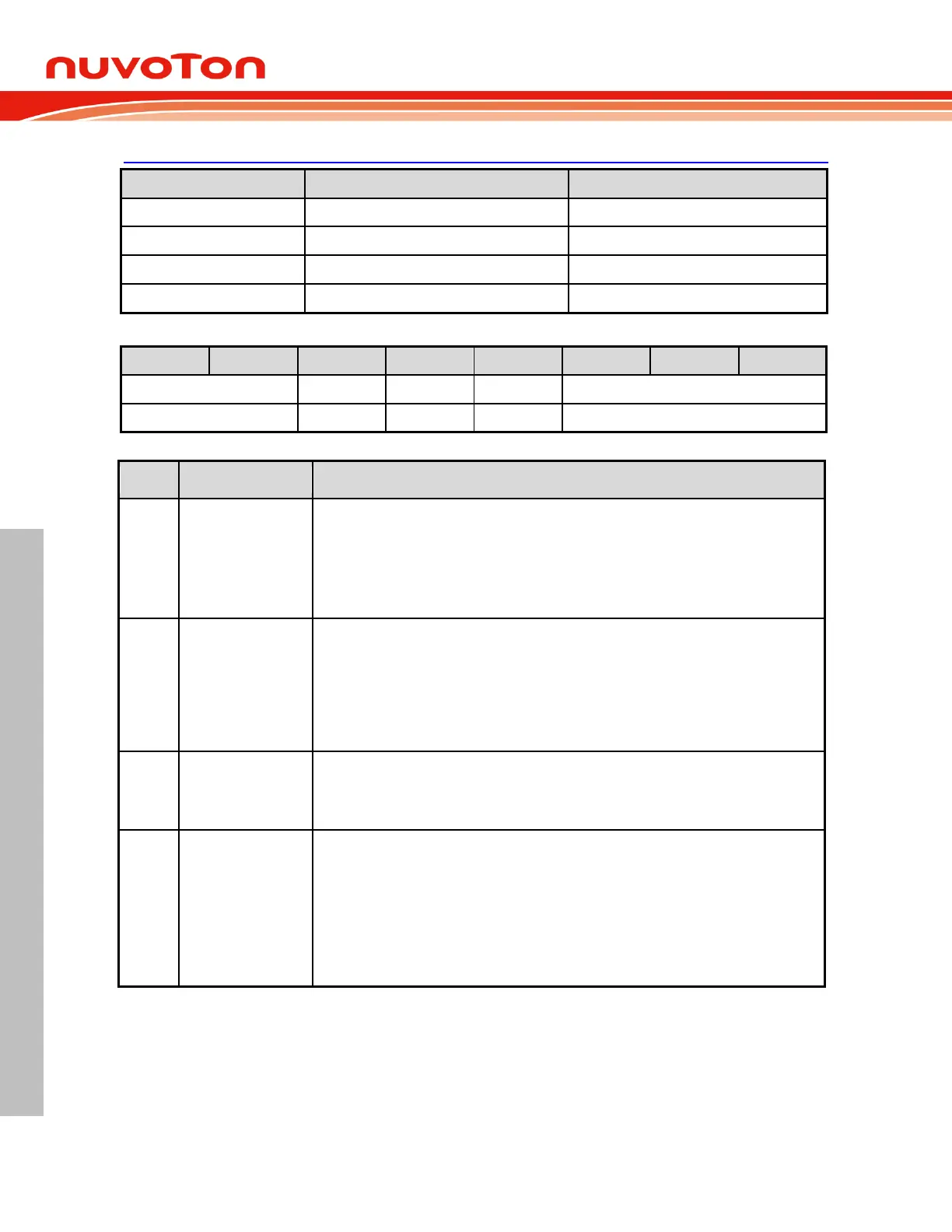

FB pin input enable

0 = PWM0 output Fault Braked by FB pin input Disabled.

1 = PWM0 output Fault Braked by FB pin input Enabled. Once an edge, which matches

FBINLS (PWM0FBD.6) selection, occurs on FB pin, PWM0 channel 0~5 output Fault

Brake data in PWM0FBD register. PWM0RUN (PWM0CON0.7) will also be

automatically cleared by hardware. The PWM0 output resumes when PWM0RUN is set

again.

Note: This bit is only valid in PWM0.

Loading...

Loading...