MS51

Nov. 28, 2019 Page 332 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

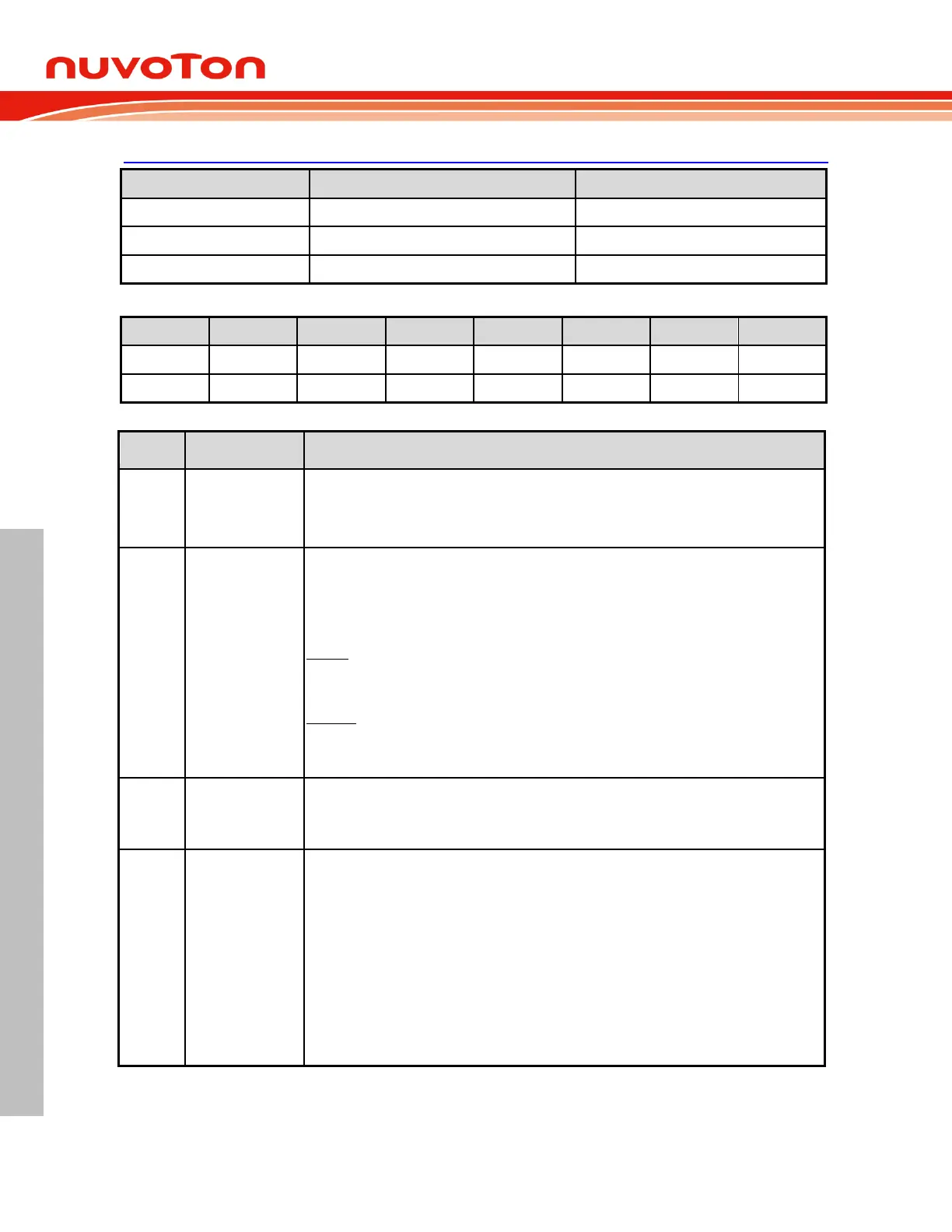

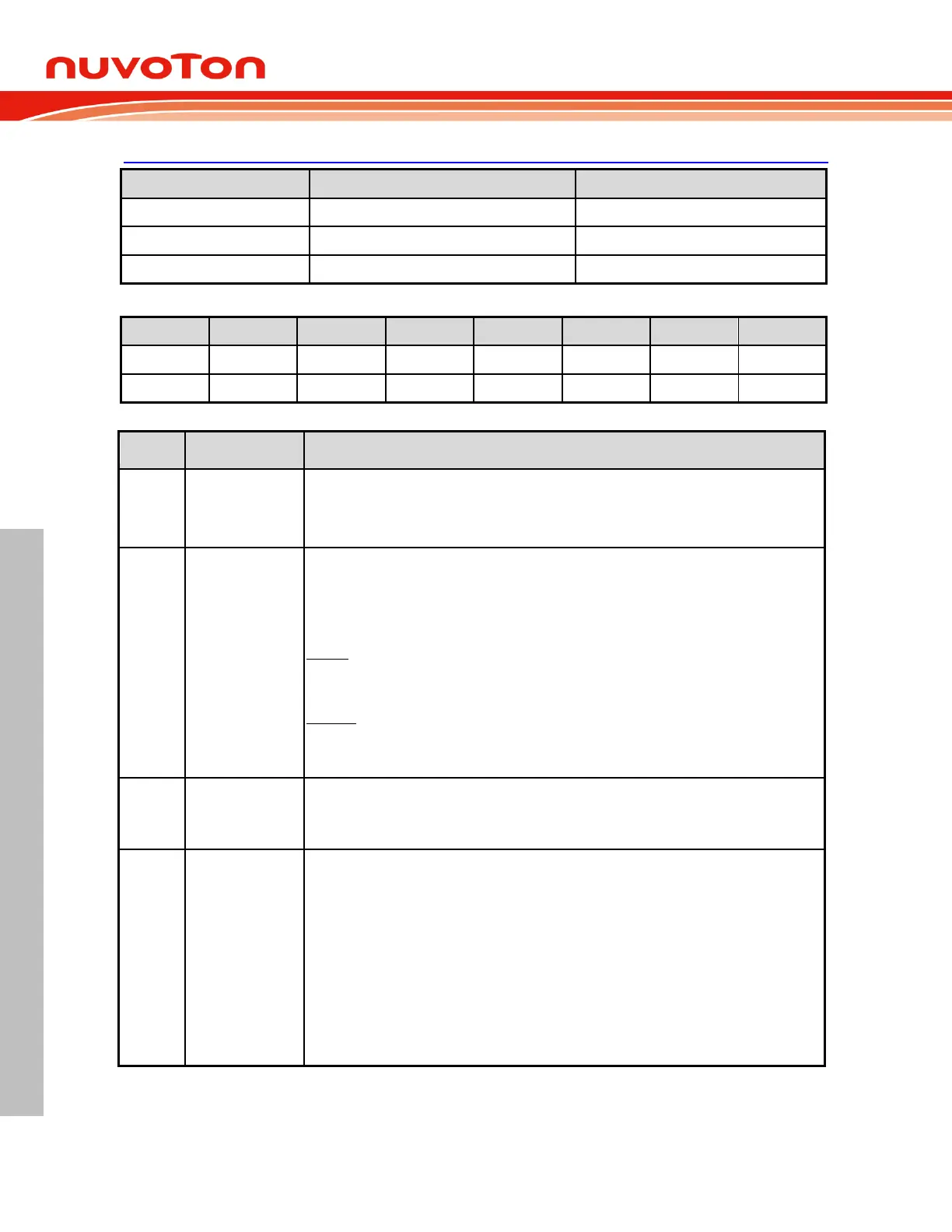

PWMnCON0 – PWMn Control 0, n = 1,2,3

PWM run enable

0 = PWM stays in idle.

1 = PWM starts running.

PWM new period and duty load

This bit is used to load period and duty control registers in their buffer if new period or duty

value needs to be updated. The loading will act while a PWM period is completed. The new

period and duty affected on the next PWM cycle. After the loading is complete, LOAD will be

automatically cleared via hardware. The meaning of writing and reading LOAD bit is different.

Writing:

0 = No effect.

1 = Load new period and duty in their buffers while a PWM period is completed.

Reading:

0 = A loading of new period and duty is finished.

1 = A loading of new period and duty is not yet finished.

PWM flag

This flag is set according to definitions of INTSEL[2:0] and INTTYP[1:0] in PWM0INTC. This

bit is cleared by software.

Clear PWM counter

Setting this bit clears the value of PWM 16-bit counter for resetting to 0000H. After the

counter value is cleared, CLRPWM will be automatically cleared via hardware. The meaning

of writing and reading CLRPWM bit is different.

Writing:

0 = No effect.

1 = Clearing PWM 16-bit counter.

Reading:

0 = PWM 16-bit counter is completely cleared.

1 = PWM 16-bit counter is not yet cleared.

Loading...

Loading...