671

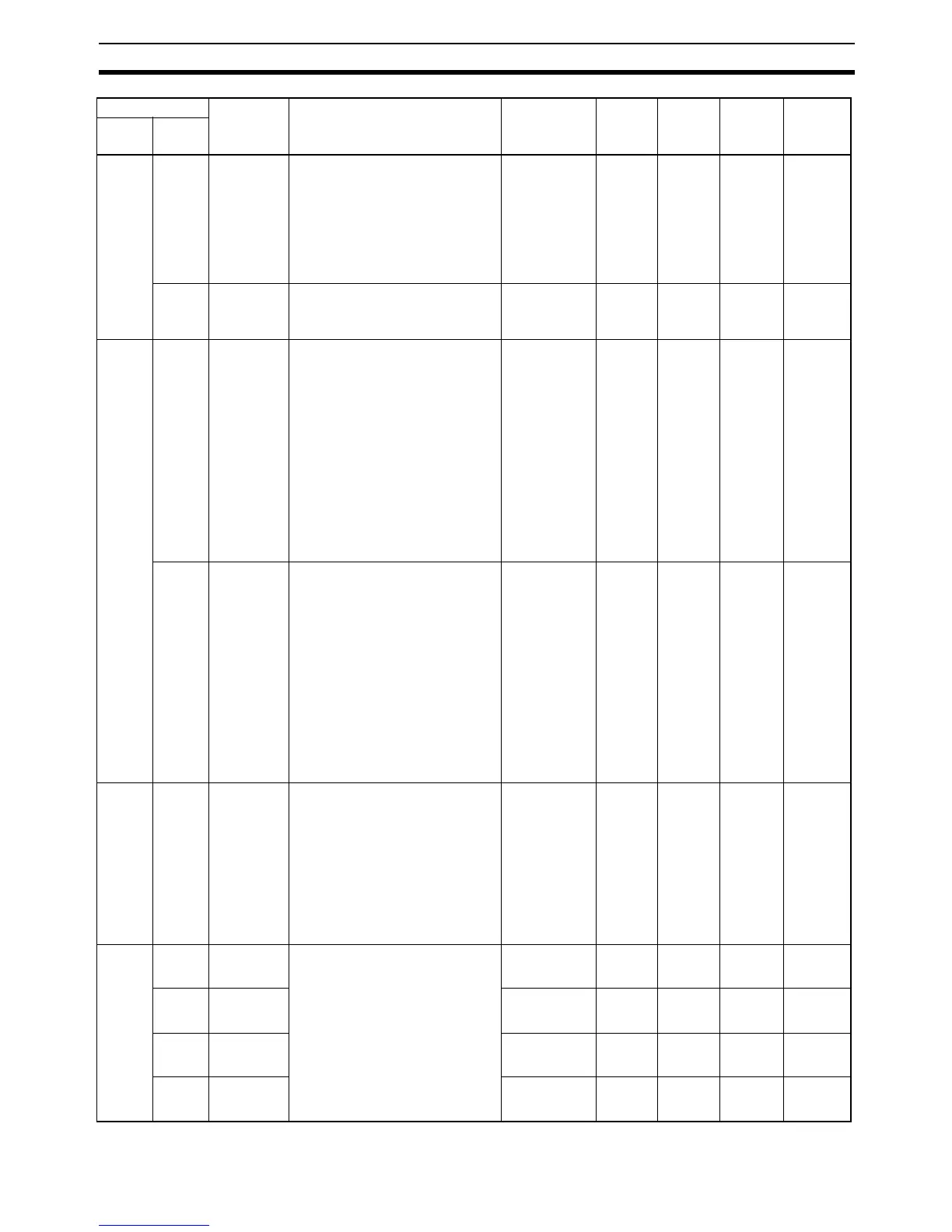

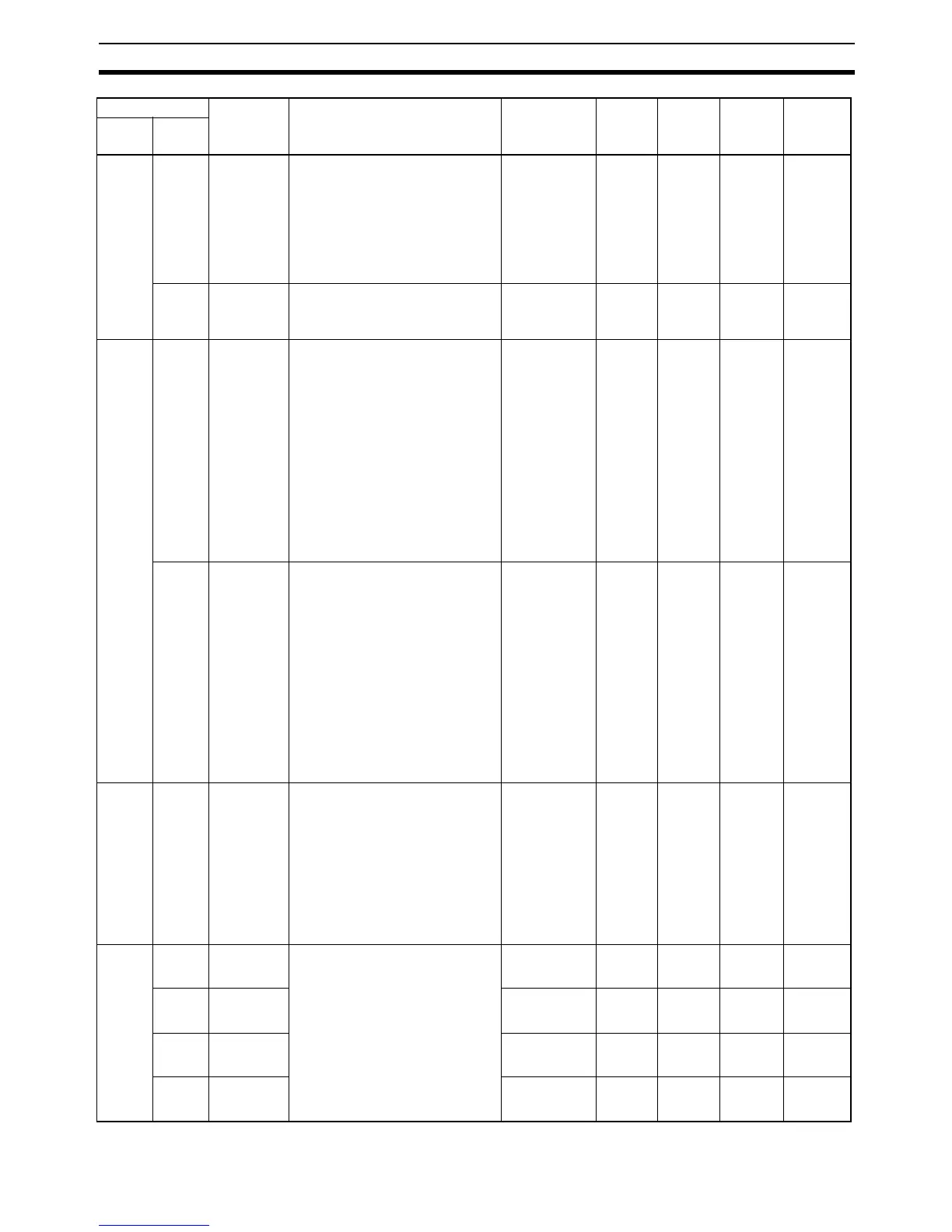

Auxiliary Area Allocations by Address Appendix D

A527 A527.00

to

A527.07

Online Edit-

ing Disable

Bit Validator

The Online Editing Disable Bit

(A527.09) is valid only when this byte

contains 5A.

To disable online editing from the

CX-Programmer, set this byte to 5A

and turn ON A527.09.

(Online editing refers to changing or

adding to the program while the PLC

is operating in MONITOR mode.)

5A:

A527.09

enabled

Other value:

A527.09 dis-

abled

Retained Cleared --- A527.09

A527.09 Online Edit-

ing Disable

Bit

Turn this bit ON to disable online

editing. The setting of this bit is valid

only when A527.00 to A527.07 have

been set to 5A.

ON: Disabled

OFF: Not dis-

abled

Retained Cleared --- A527.00

to

A527.07

A528 A528.00

to

A528.07

Serial Port 2

Error Flags

These flags indicate what kind of

error has occurred at the serial port

2; they are automatically turned OFF

when the serial port 2 is restarted.

(These flags are not valid in periph-

eral bus mode and only bit 5 is valid

in NT Link mode.)

PLC Link Polling Unit:

Bit 05: ON for timeout error.

PLC Link Polled Unit:

Bit 03: ON for framing error.

Bit 04: ON for overrun error.

Bit 05: ON for timeout error.

These bits can be cleared by the CX-

Programmer.

Bits 00 and 01:

Not used.

Bit 02: ON for

parity error.

Bit 03: ON for

framing error.

Bit 04: ON for

overrun error.

Bit 05: ON for

timeout error.

Bits 06 and 07:

Not used.

--- --- --- ---

A528.08

to

A528.15

Serial Port 1

Error Code

These flags indicate what kind of

error has occurred at the serial port

1; they are automatically turned OFF

when the serial port 1 is restarted.

(These flags are not valid in periph-

eral bus mode and only bit 5 is valid

in NT Link mode.)

PLC Link Polling Unit:

Bit 13: ON for timeout error.

PLC Link Polled Unit:

Bit 11: ON for framing error.

Bit 12: ON for overrun error.

Bit 13: ON for timeout error.

These bits can be cleared by the CX-

Programmer.

Bits 08 and 09:

Not used.

Bit 10: ON for

parity error.

Bit 11: ON for

framing error.

Bit 12: ON for

overrun error.

Bit 13: ON for

timeout error.

Bits 14 and 15:

Not used.

--- --- --- ---

A529 All FAL/FALS

Number for

System

Error Simu-

lation

Set a dummy FAL/FALS number to

use to simulate the system error

using FAL(006) or FALS(007).

When FAL(006) or FALS(007) is exe-

cuted and the number in A529 is the

same as the one specified in the

operand of the instruction, the sys-

tem error given in the operand of the

instruction will be generated instead

of a user-defined error.

0001 to 01FF

hex: FAL/FALS

numbers 1 to

511

0000 or 0200

to FFFF hex:

No FAL/FALS

number for sys-

tem error simu-

lation. (No error

will be gener-

ated.)

Retained Cleared --- ---

A531 A531.00 High-speed

Counter 0

Reset Bit

When the reset method is set to

Phase-Z signal + Software reset, the

corresponding high-speed counter's

PV will be reset if the phase-Z signal

is received while this bit is ON.

When the reset method is set to Soft-

ware reset, the corresponding high-

speed counter's PV will be reset in

the cycle when this bit turns ON.

--- Retained Cleared --- ---

A531.01 High-speed

Counter 1

Reset Bit

--- Retained Cleared --- ---

A531.02 High-speed

Counter 2

Reset Bit

--- Retained Cleared --- ---

A531.03 High-speed

Counter 3

Reset Bit

--- Retained Cleared --- ---

Addresses Name Function Settings Status

after

mode

change

Status at

startup

Write

timing

Related

Flags,

Settings

Word Bits

Loading...

Loading...