4.13

Date Code 20020903 SEL-587Z Instruction Manual

Control Logic

SEL

OGIC Control Equations

Processing Order and Processing Interval

The relay elements and logic (and corresponding SELOGIC control equation

settings and resultant Relay Word bits) are processed in the order shown in

Tab le 4. 7 (top to bottom). The relay processing interval is every 1/8-cycle, and

the Relay Word bit states (logical 1 or logical 0) are updated with each

1/8-cycle pass. Once a Relay Word bit is updated during a 1/8-cycle pass, it

retains the state (logical 1 or logical 0) until updated again on the next

1/8-cycle pass.

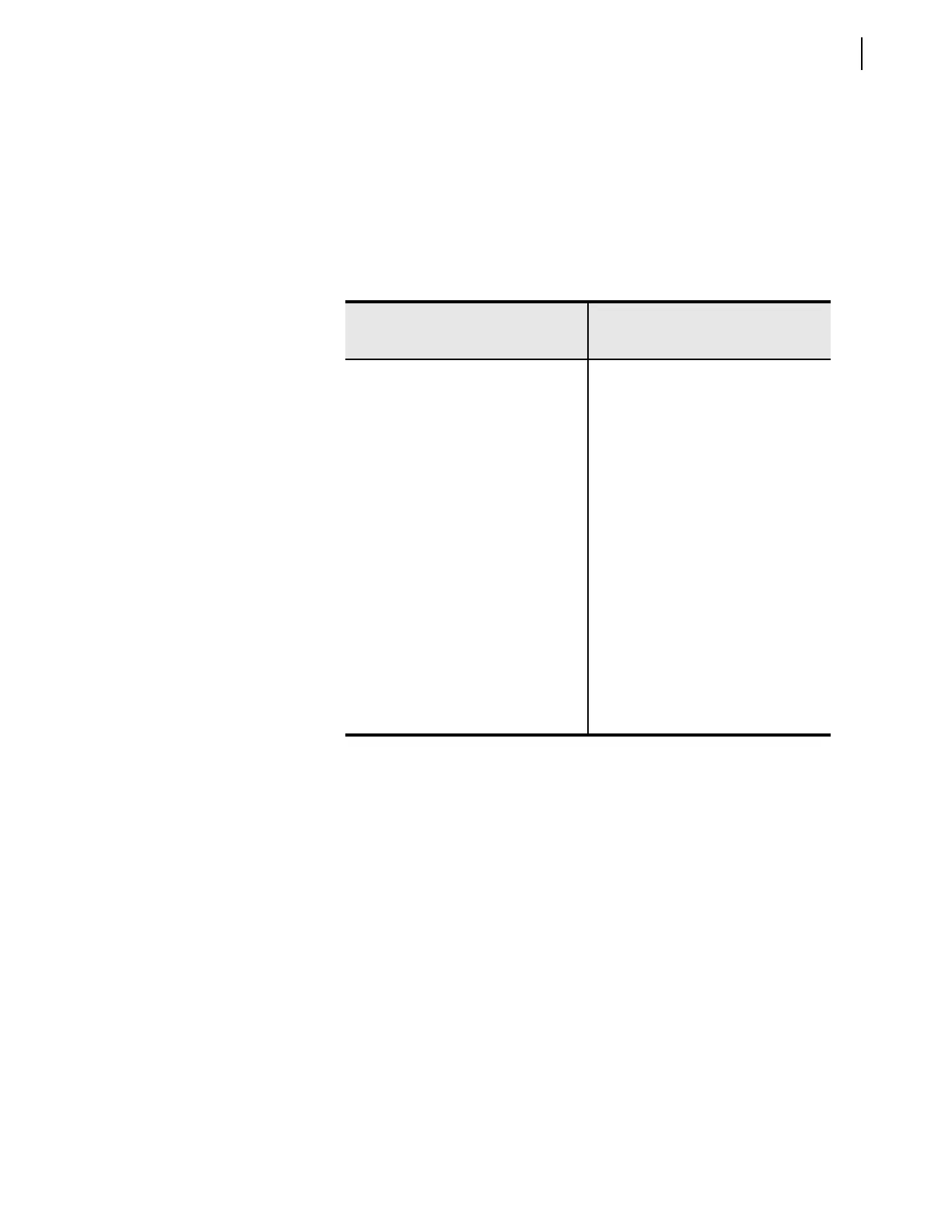

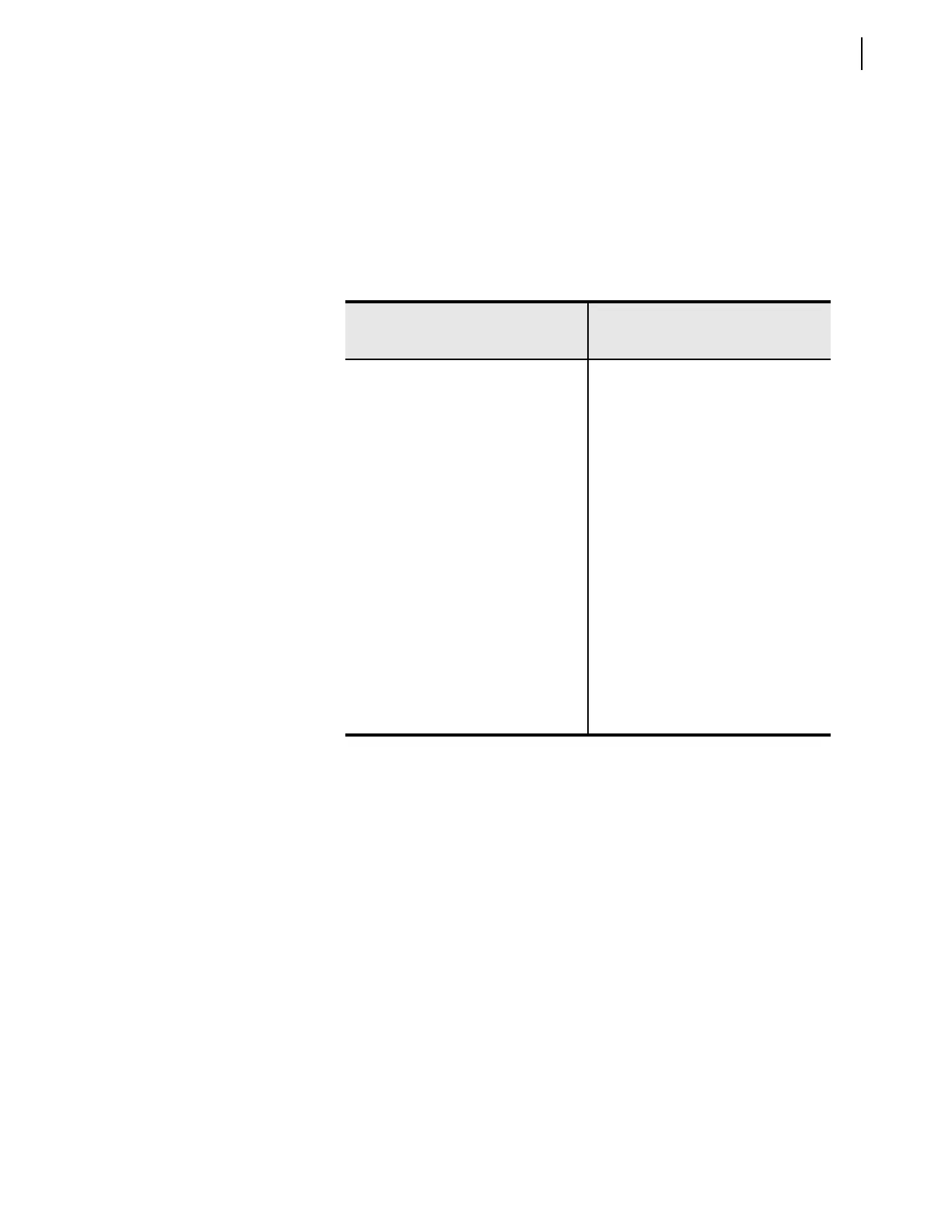

Table 4.7 Processing Order of Relay Elements and Logic (top to bottom)

Relay Elements and Logic

(corresponding SEL

OGIC control

equations listed in parentheses)

Relay Word Bits

Local Control Switches LB1–LB8

Remote Control Switches RB1–RB8

Optoisolated Inputs IN1, IN2

Demand Ammetering PDEM, GDEM, QDEM

Differential Elements 87A1, 87A2, 87B1, 87B2, 87C1, 87C2

Instantaneous Overcurrent Elements 50P1–50P3, 50A1, 50B1, 50C1, 50A2,

50B2, 50C2, 50G1, 50G2, 50Q1, 50Q2

Time-Overcurrent Elements

51PTC, 51ATC, 51BTC,

51CTC, 51GTC, 51QTC

51P, 51PT, 51PR, 51A, 51AT, 51AR,

51B, 51BT, 51BR, 51C, 51CT, 51CR,

51G, 51GT, 51GR, 51Q, 51QT, 51QR

Trip Logic (TR1, 2, 3; ULTR1, 2 , 3) TRIP1, TRIP2, TRIP3

Close Logic (52A, CL, ULCL) CLOSE, CF

SEL

OGIC Control Equation

Variables/Timers (SV1–SV14)

SV1–SV14, SV5T–SV14T

Output Contacts (OUT1–OUT4) OUT1–OUT4

Display Points (DP1–DP8)

Event Report Triggers (ER1, ER2)

Loading...

Loading...