89

83507013 Rev G

7.11.4 Service Request: Enable and Event Registers

The conditional Registers are continuously monitored. When a change is detected in a

register bit which is enabled, the power supply will generate an SRQ message.

The SRQ message is: “!nn” terminated by CR, where the nn is the power supply

address. The SRQ will be generated either in Local or Remote mode.

Refer to Tables 7-10 to 7-13 for details of the Enable and Event registers. Refer to

Section 7.9.4. for SRQ information.

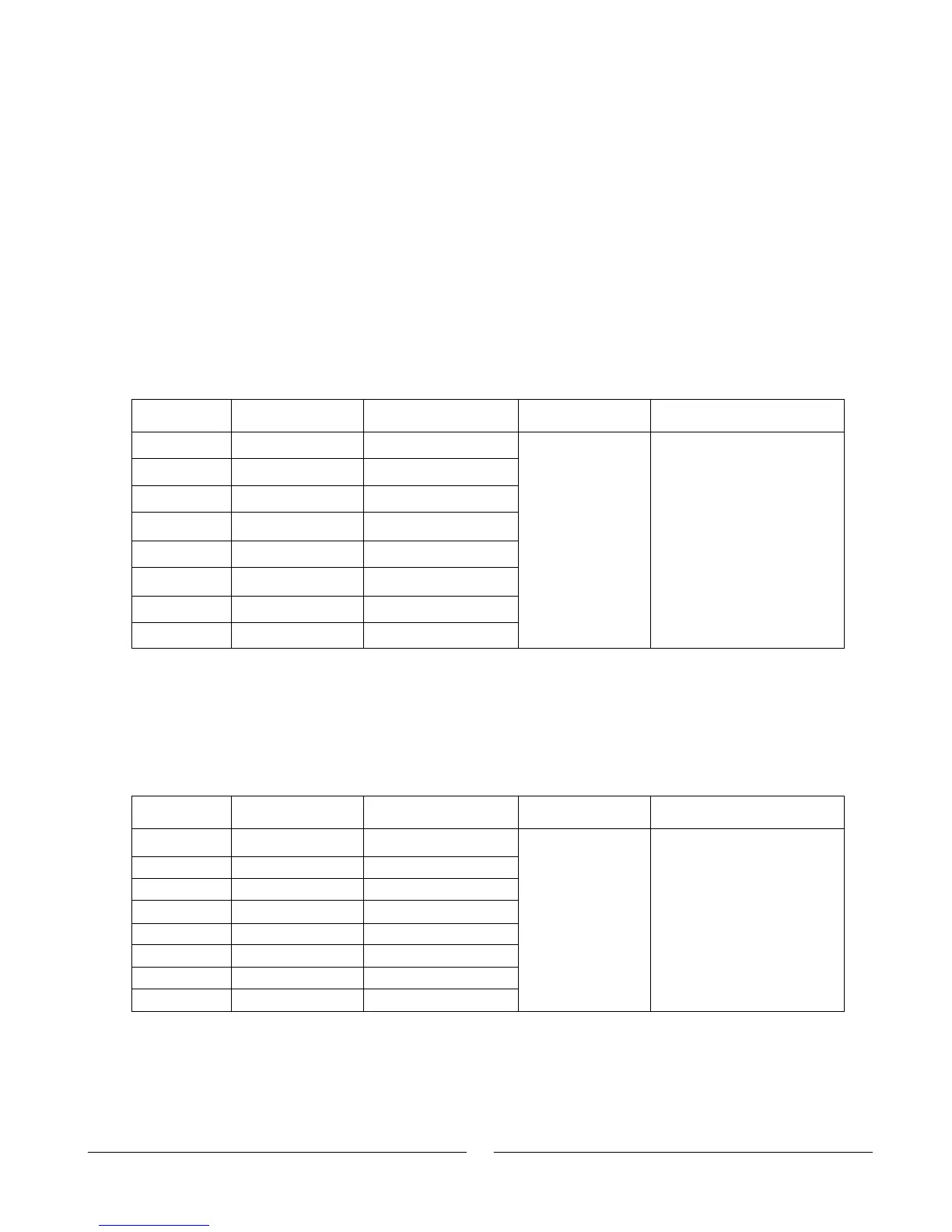

1. Fault Enable Register (FENA nn, FENA?)

The Fault Enable Register is set to the enable faults SRQs.

Table 7-10: Fault Enable Register

User command:

“FENA nn” where

nn is hexadecimal

User command: “FENA nn”

where nn is hexadecimal (if

nn=”00”, no fault SRQs will

be generated).

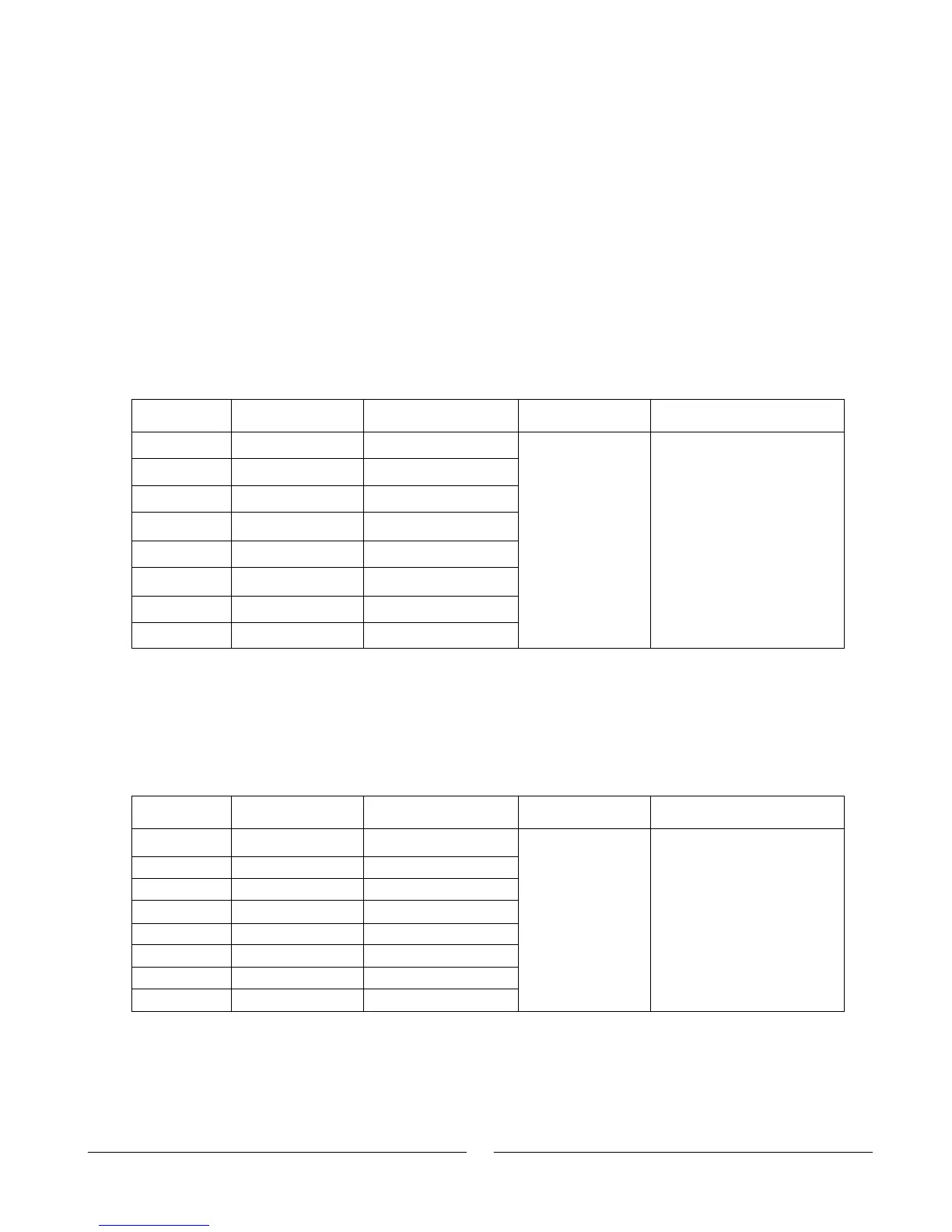

2. Fault Event Register (FEVE?)

The Fault Event will set a bit if a condition occurs and it is Enabled. The register is cleared when

FEVE?, CLS or RST commands are received.

Table 7-11: Fault Event Register

Fault condition

occurs and it is

enabled.

The fault can set a

bit, but when the

fault clears the bit

remains set.

Entire Event Register is

cleared when user sends

“FEVE?” command to read

the register.

“CLS” and power-up also

clear the Fault Event

Register. (The Fault Event

Register is not cleared by

RST)

Loading...

Loading...