Description of CEI-100/200 ARINC Interface Programming the ARINC Channel Setup

CEI-100/CEI-200/CEI-x20 User’s Manual 161

Programming the ARINC Channel Setup

An integrated control chip set which controls 2 receive channels controls

all ARINC channels and 1 transmit channel. Each chip set is programmed

with a separate control word that is formatted as follows:

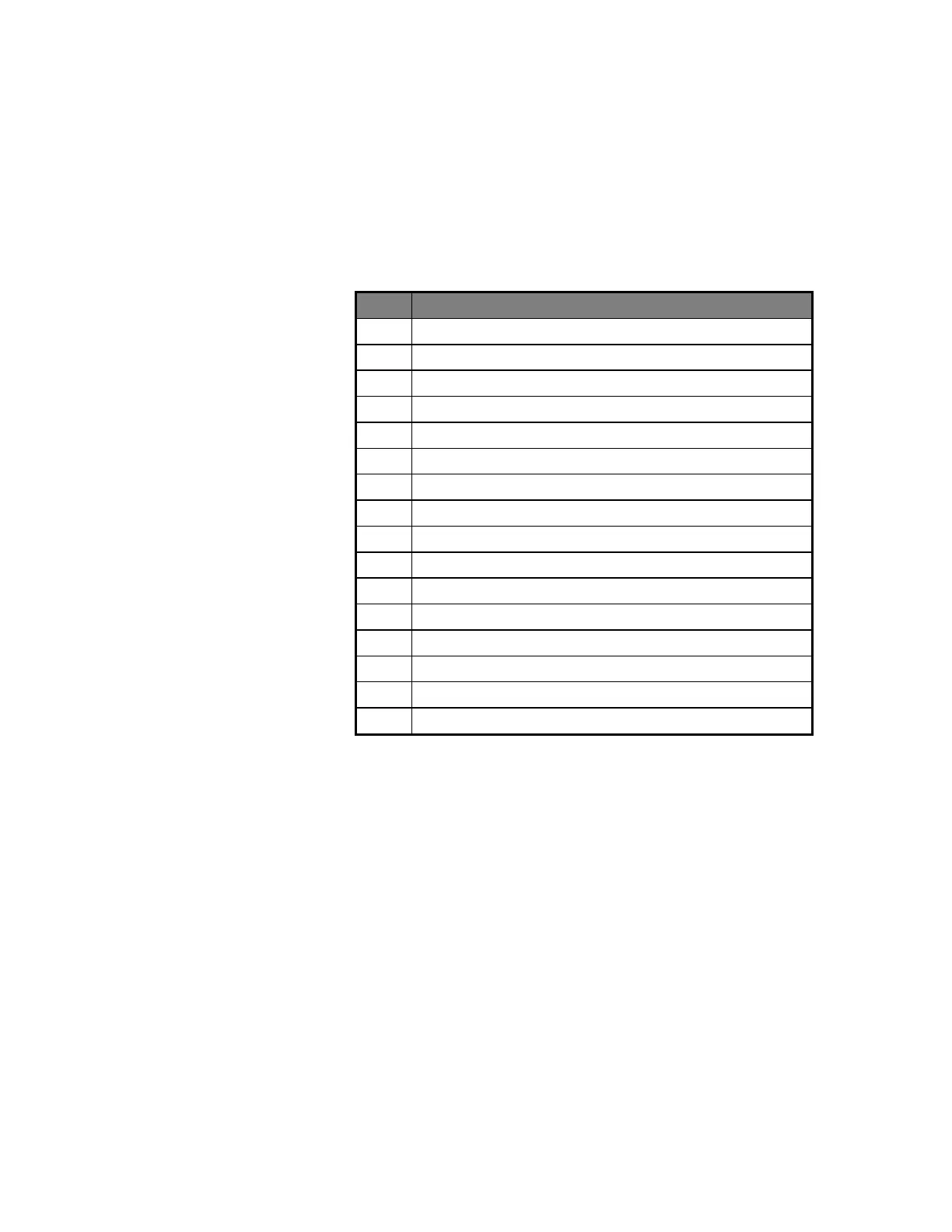

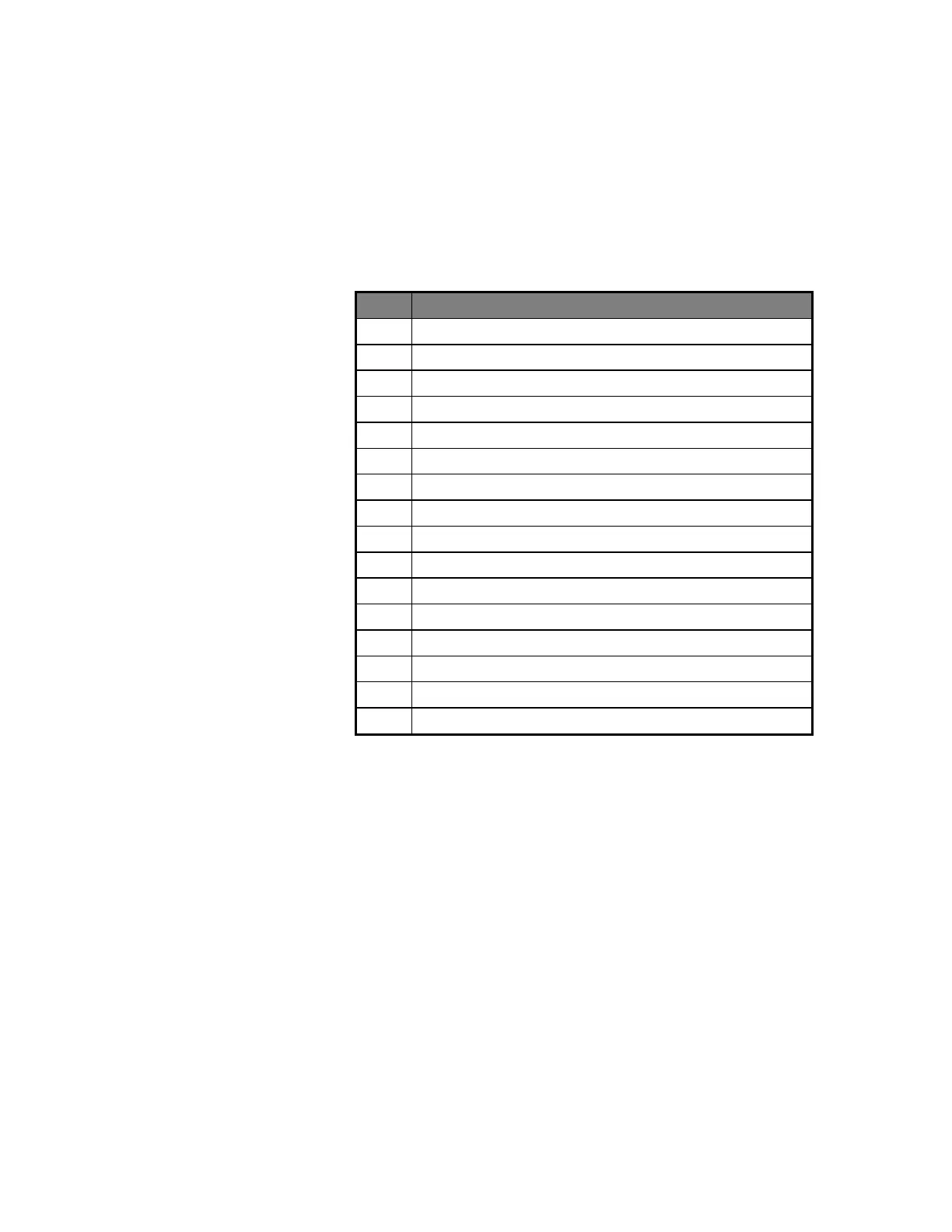

Table 47. Control Word Format

Internal Wrap-around enable (0 = enable, 1 = disable)

Receiver 1 SDI pre-filter (0=disable, 1= enable)

Receiver 1 SDI pre-filter mask LS bit

Receiver 1 SDI pre-filter mask MS bit

Receiver 2 SDI pre-filter (0=disable, 1=enable)

Receiver 2 SDI pre-filter mask LS bit

Receiver 2 SDI pre-filter mask MS bit

Transmit parity (0 = odd parity, 1 = even parity)

Transmit bit rate (0 = 100K Bps, 1 = 12.5K Bps)

Receiver bit rate (0 = 100K Bps, 1 = 12.5K Bps)

If SDI filtering is enabled on a channel, the received SDI must match that

channel’s two pre-filter mask bits. If internal self-test is enabled, the data

for a transmit channel is tied internally to both of its corresponding receive

channels. For example, on transmit channel 2, receive channel 3 gets the

transmitted data and receive channel 4 gets the inverted data.

The control words are located in the following dual-port memory offset

locations:

CEI-100 - 044Eh

CEI-200 - 04A2h (chip set 1 - receivers 1,2 transmitter 1)

04A4h (chip set 2 - receivers 3,4 transmitter 2)

04A6h (chip set 3 - receivers 5,6 transmitter 3)

04A8h (chip set 4 - receivers 7,8 transmitter 4)

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...